2

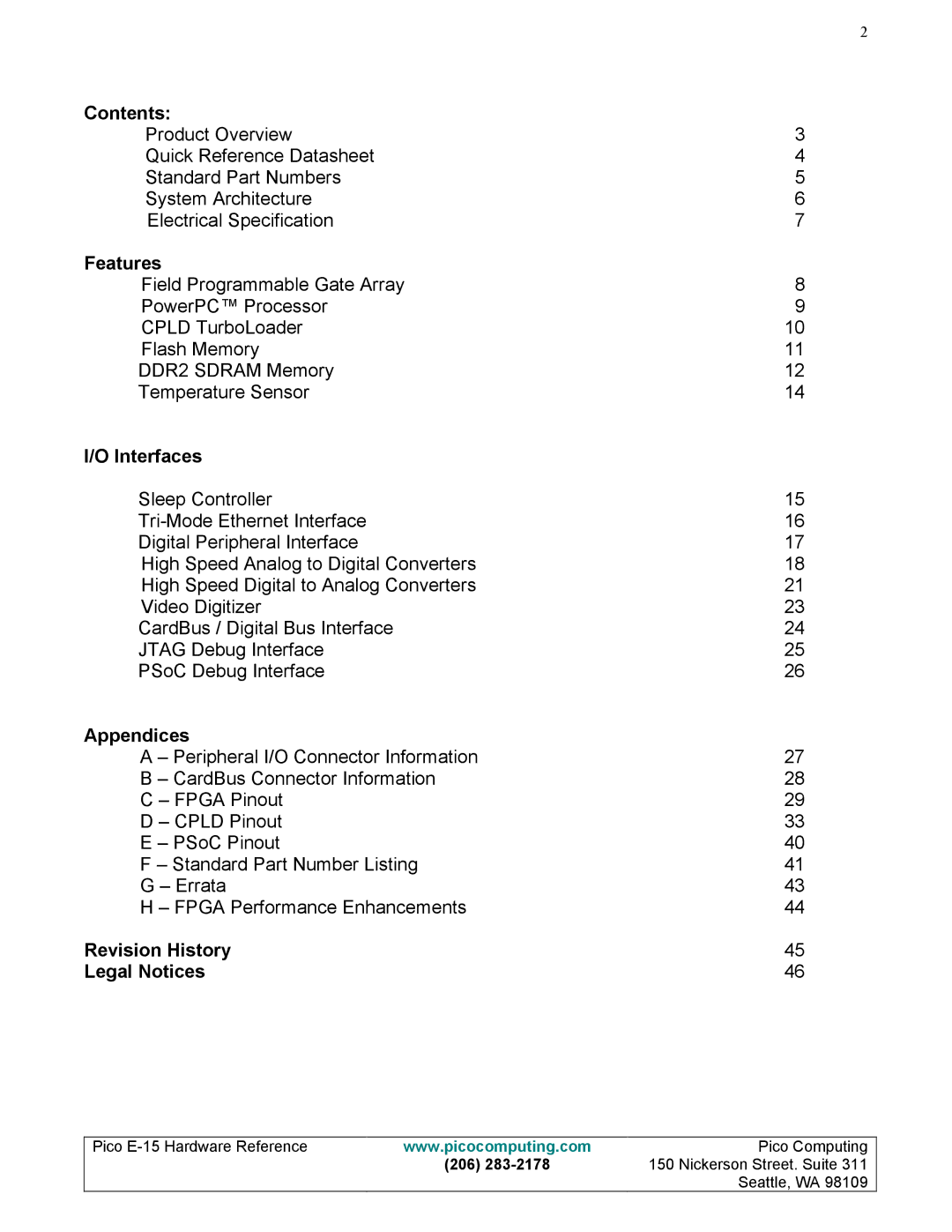

Contents: |

|

Product Overview | 3 |

Quick Reference Datasheet | 4 |

Standard Part Numbers | 5 |

System Architecture | 6 |

Electrical Specification | 7 |

Features |

|

Field Programmable Gate Array | 8 |

PowerPC™ Processor | 9 |

CPLD TurboLoader | 10 |

Flash Memory | 11 |

DDR2 SDRAM Memory | 12 |

Temperature Sensor | 14 |

I/O Interfaces |

|

Sleep Controller | 15 |

16 | |

Digital Peripheral Interface | 17 |

High Speed Analog to Digital Converters | 18 |

High Speed Digital to Analog Converters | 21 |

Video Digitizer | 23 |

CardBus / Digital Bus Interface | 24 |

JTAG Debug Interface | 25 |

PSoC Debug Interface | 26 |

Appendices |

|

A – Peripheral I/O Connector Information | 27 |

B – CardBus Connector Information | 28 |

C – FPGA Pinout | 29 |

D – CPLD Pinout | 33 |

E – PSoC Pinout | 40 |

F – Standard Part Number Listing | 41 |

G – Errata | 43 |

H – FPGA Performance Enhancements | 44 |

Revision History | 45 |

Legal Notices | 46 |

Pico | www.picocomputing.com | Pico Computing |

| (206) | 150 Nickerson Street. Suite 311 |

|

| Seattle, WA 98109 |