37

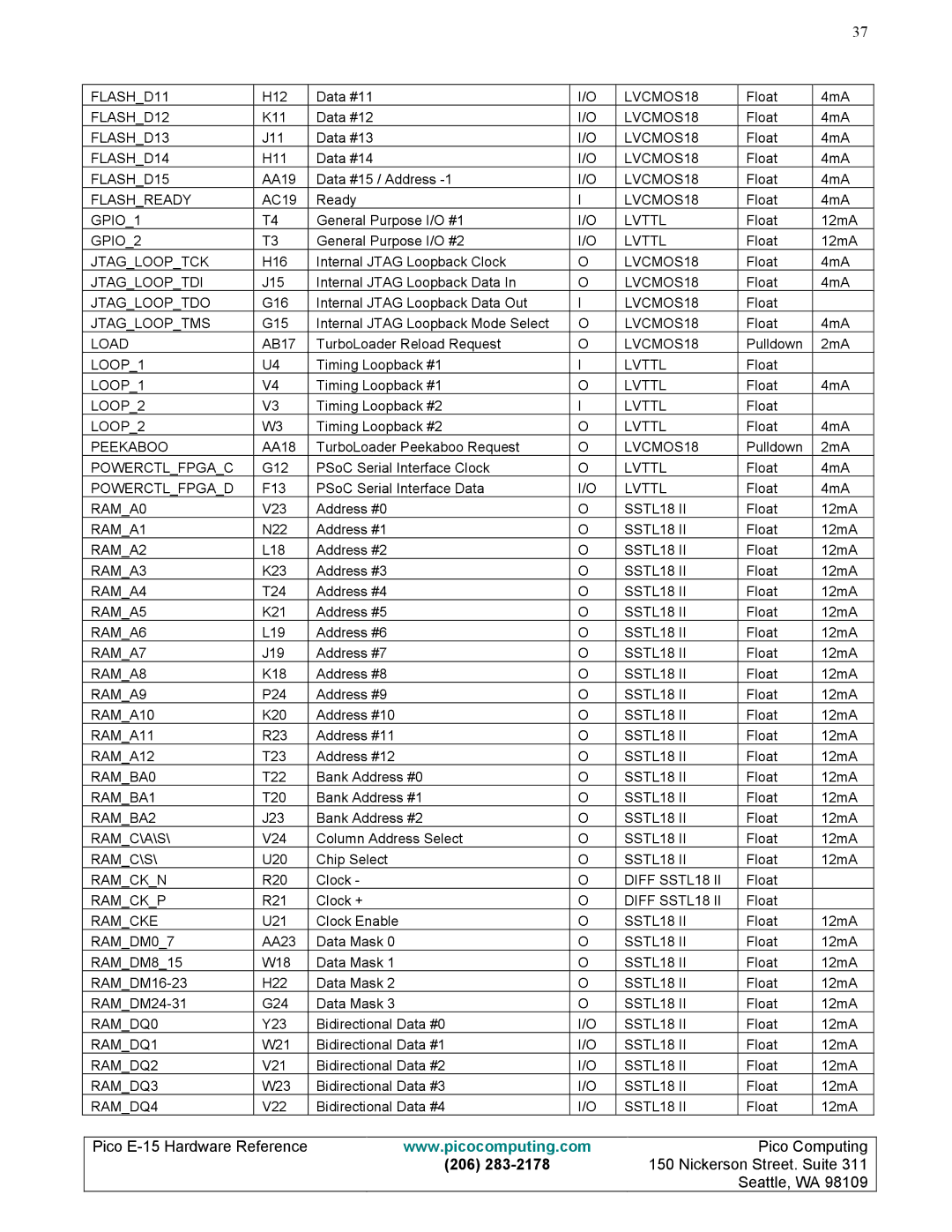

FLASH_D11 | H12 | Data #11 | I/O | LVCMOS18 | Float | 4mA |

FLASH_D12 | K11 | Data #12 | I/O | LVCMOS18 | Float | 4mA |

FLASH_D13 | J11 | Data #13 | I/O | LVCMOS18 | Float | 4mA |

FLASH_D14 | H11 | Data #14 | I/O | LVCMOS18 | Float | 4mA |

FLASH_D15 | AA19 | Data #15 / Address | I/O | LVCMOS18 | Float | 4mA |

FLASH_READY | AC19 | Ready | I | LVCMOS18 | Float | 4mA |

GPIO_1 | T4 | General Purpose I/O #1 | I/O | LVTTL | Float | 12mA |

GPIO_2 | T3 | General Purpose I/O #2 | I/O | LVTTL | Float | 12mA |

JTAG_LOOP_TCK | H16 | Internal JTAG Loopback Clock | O | LVCMOS18 | Float | 4mA |

JTAG_LOOP_TDI | J15 | Internal JTAG Loopback Data In | O | LVCMOS18 | Float | 4mA |

JTAG_LOOP_TDO | G16 | Internal JTAG Loopback Data Out | I | LVCMOS18 | Float |

|

JTAG_LOOP_TMS | G15 | Internal JTAG Loopback Mode Select | O | LVCMOS18 | Float | 4mA |

LOAD | AB17 | TurboLoader Reload Request | O | LVCMOS18 | Pulldown | 2mA |

LOOP_1 | U4 | Timing Loopback #1 | I | LVTTL | Float |

|

LOOP_1 | V4 | Timing Loopback #1 | O | LVTTL | Float | 4mA |

LOOP_2 | V3 | Timing Loopback #2 | I | LVTTL | Float |

|

LOOP_2 | W3 | Timing Loopback #2 | O | LVTTL | Float | 4mA |

PEEKABOO | AA18 | TurboLoader Peekaboo Request | O | LVCMOS18 | Pulldown | 2mA |

POWERCTL_FPGA_C | G12 | PSoC Serial Interface Clock | O | LVTTL | Float | 4mA |

POWERCTL_FPGA_D | F13 | PSoC Serial Interface Data | I/O | LVTTL | Float | 4mA |

RAM_A0 | V23 | Address #0 | O | SSTL18 II | Float | 12mA |

RAM_A1 | N22 | Address #1 | O | SSTL18 II | Float | 12mA |

RAM_A2 | L18 | Address #2 | O | SSTL18 II | Float | 12mA |

RAM_A3 | K23 | Address #3 | O | SSTL18 II | Float | 12mA |

RAM_A4 | T24 | Address #4 | O | SSTL18 II | Float | 12mA |

RAM_A5 | K21 | Address #5 | O | SSTL18 II | Float | 12mA |

RAM_A6 | L19 | Address #6 | O | SSTL18 II | Float | 12mA |

RAM_A7 | J19 | Address #7 | O | SSTL18 II | Float | 12mA |

RAM_A8 | K18 | Address #8 | O | SSTL18 II | Float | 12mA |

RAM_A9 | P24 | Address #9 | O | SSTL18 II | Float | 12mA |

RAM_A10 | K20 | Address #10 | O | SSTL18 II | Float | 12mA |

RAM_A11 | R23 | Address #11 | O | SSTL18 II | Float | 12mA |

RAM_A12 | T23 | Address #12 | O | SSTL18 II | Float | 12mA |

RAM_BA0 | T22 | Bank Address #0 | O | SSTL18 II | Float | 12mA |

RAM_BA1 | T20 | Bank Address #1 | O | SSTL18 II | Float | 12mA |

RAM_BA2 | J23 | Bank Address #2 | O | SSTL18 II | Float | 12mA |

RAM_C\A\S\ | V24 | Column Address Select | O | SSTL18 II | Float | 12mA |

RAM_C\S\ | U20 | Chip Select | O | SSTL18 II | Float | 12mA |

RAM_CK_N | R20 | Clock - | O | DIFF SSTL18 II | Float |

|

RAM_CK_P | R21 | Clock + | O | DIFF SSTL18 II | Float |

|

RAM_CKE | U21 | Clock Enable | O | SSTL18 II | Float | 12mA |

RAM_DM0_7 | AA23 | Data Mask 0 | O | SSTL18 II | Float | 12mA |

RAM_DM8_15 | W18 | Data Mask 1 | O | SSTL18 II | Float | 12mA |

H22 | Data Mask 2 | O | SSTL18 II | Float | 12mA | |

G24 | Data Mask 3 | O | SSTL18 II | Float | 12mA | |

RAM_DQ0 | Y23 | Bidirectional Data #0 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ1 | W21 | Bidirectional Data #1 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ2 | V21 | Bidirectional Data #2 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ3 | W23 | Bidirectional Data #3 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ4 | V22 | Bidirectional Data #4 | I/O | SSTL18 II | Float | 12mA |

Pico | www.picocomputing.com | Pico Computing |

| (206) | 150 Nickerson Street. Suite 311 |

|

| Seattle, WA 98109 |