CY7C604XX

enCoRe™ V Low Voltage Microcontroller

Features

■Powerful Harvard Architecture Processor

❐M8C processor speeds running up to 24 MHz

❐Low power at high processing speeds

❐Interrupt controller

❐1.71V to 3.6V operating voltage

❐Temperature range: 0°C to 70°C

■Flexible

❐Up to 32K Flash program storage

•50,000 Erase and write cycles

•Flexible protection modes

❐Up to 2048 bytes SRAM data storage

❐

■Complete Development Tools

❐Free development tool (PSoC Designer™)

❐Full featured,

❐Full speed emulation

❐Complex breakpoint structure

❐128K trace memory

■Precision, Programmable Clocking

❐

❐Internal ±5.0% 6, 12, or 24 MHz main oscillator

❐Internal low speed oscillator at 32 kHz for watchdog and sleep.The frequency range is 19 to 50 kHz with a 32 kHz typical value

■Programmable Pin Configurations

❐25 mA sink current on all GPIO

❐Pull Up, High Z, Open Drain, CMOS drive modes on all GPIO

❐Configurable inputs on all GPIO

❐Low dropout voltage regulator for Port 1 pins. Programmable to output 3.0, 2.5, or 1.8V at the I/O pins

❐Selectable, regulated digital I/O on Port 1

•Configurable input threshold for Port 1

•3.0V, 20 mA total Port 1 source current

•

❐5 mA strong drive mode on Ports 0 and 1

■Additional System Resources

❐Configurable communication speeds

❐I2C Slave

•Selectable to 50 kHz, 100 kHz, or 400 kHz

•Implementation requires no clock stretching

•Implementation during sleep modes with less than 100 mA

•Hardware address detection

❐SPI master and SPI slave

•Configurable between 93.75 kHz and 12 MHz

❐Three

❐

❐Watchdog and sleep timers

❐Integrated supervisory circuit

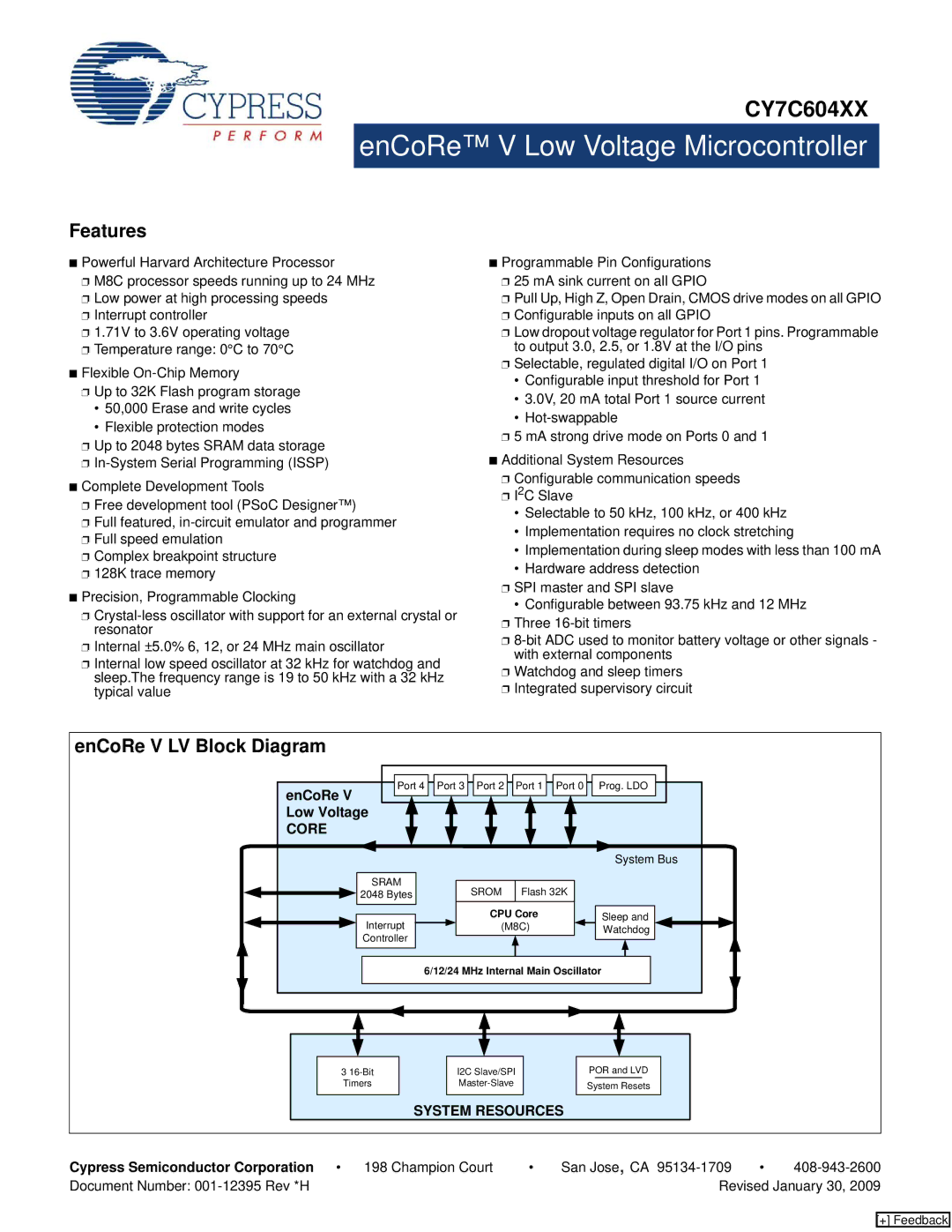

enCoRe V LV Block Diagram

enCoRe V | Port 4 | Port 3 | Port 2 | Port 1 | Port 0 | Prog. LDO |

|

|

|

|

|

| |

Low Voltage |

|

|

|

|

| |

CORE |

|

|

|

|

|

|

|

|

|

|

|

| System Bus |

| SRAM |

| SROM | Flash 32K |

| |

| 2048 Bytes |

|

| |||

| Interrupt |

| CPU Core |

| Sleep and | |

|

| (M8C) |

| Watchdog | ||

| Controller |

|

|

|

|

|

| 6/12/24 MHz Internal Main Oscillator | |||||

3

I2C Slave/SPI

SYSTEM RESOURCES

POR and LVD

System Resets

Cypress Semiconductor Corporation • 198 Champion Court | • | San Jose, CA | • | |

Document Number: |

| Revised January 30, 2009 | ||

[+] Feedback