CY7C604XX

Document History Page

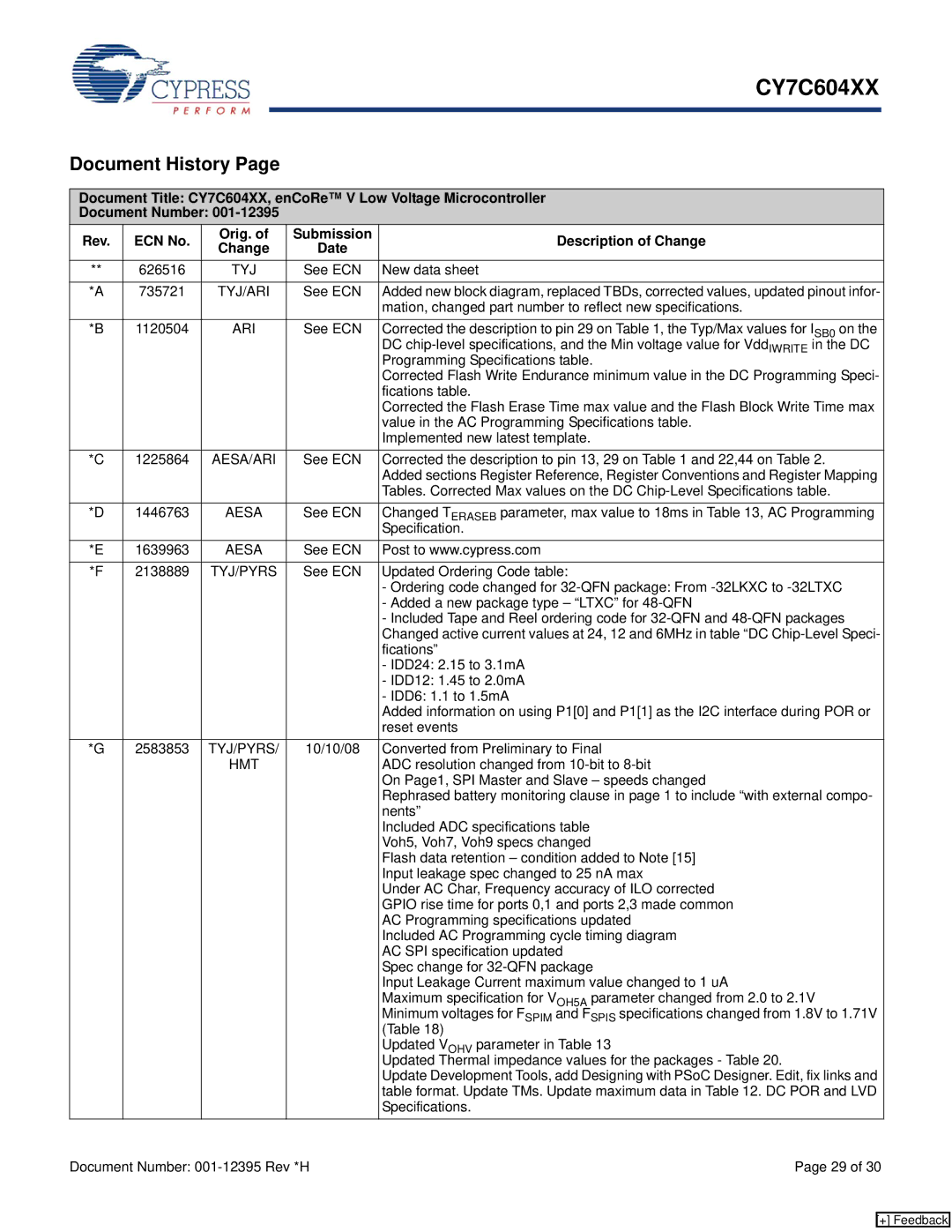

Document Title: CY7C604XX, enCoRe™ V Low Voltage Microcontroller | |||||

Document Number: |

|

| |||

Rev. | ECN No. | Orig. of | Submission | Description of Change | |

Change | Date | ||||

|

|

| |||

** | 626516 | TYJ | See ECN | New data sheet | |

|

|

|

|

| |

*A | 735721 | TYJ/ARI | See ECN | Added new block diagram, replaced TBDs, corrected values, updated pinout infor- | |

|

|

|

| mation, changed part number to reflect new specifications. | |

*B | 1120504 | ARI | See ECN | Corrected the description to pin 29 on Table 1, the Typ/Max values for ISB0 on the | |

|

|

|

| DC | |

|

|

|

| Programming Specifications table. | |

|

|

|

| Corrected Flash Write Endurance minimum value in the DC Programming Speci- | |

|

|

|

| fications table. | |

|

|

|

| Corrected the Flash Erase Time max value and the Flash Block Write Time max | |

|

|

|

| value in the AC Programming Specifications table. | |

|

|

|

| Implemented new latest template. | |

*C | 1225864 | AESA/ARI | See ECN | Corrected the description to pin 13, 29 on Table 1 and 22,44 on Table 2. | |

|

|

|

| Added sections Register Reference, Register Conventions and Register Mapping | |

|

|

|

| Tables. Corrected Max values on the DC | |

*D | 1446763 | AESA | See ECN | Changed TERASEB parameter, max value to 18ms in Table 13, AC Programming | |

|

|

|

| Specification. | |

*E | 1639963 | AESA | See ECN | Post to www.cypress.com | |

|

|

|

|

| |

*F | 2138889 | TYJ/PYRS | See ECN | Updated Ordering Code table: | |

|

|

|

| - Ordering code changed for | |

|

|

|

| - Added a new package type – “LTXC” for | |

|

|

|

| - Included Tape and Reel ordering code for | |

|

|

|

| Changed active current values at 24, 12 and 6MHz in table “DC | |

|

|

|

| fications” | |

|

|

|

| - IDD24: 2.15 to 3.1mA | |

|

|

|

| - IDD12: 1.45 to 2.0mA | |

|

|

|

| - IDD6: 1.1 to 1.5mA | |

|

|

|

| Added information on using P1[0] and P1[1] as the I2C interface during POR or | |

|

|

|

| reset events | |

*G | 2583853 | TYJ/PYRS/ | 10/10/08 | Converted from Preliminary to Final | |

|

| HMT |

| ADC resolution changed from | |

|

|

|

| On Page1, SPI Master and Slave – speeds changed | |

|

|

|

| Rephrased battery monitoring clause in page 1 to include “with external compo- | |

|

|

|

| nents” | |

|

|

|

| Included ADC specifications table | |

|

|

|

| Voh5, Voh7, Voh9 specs changed | |

|

|

|

| Flash data retention – condition added to Note [15] | |

|

|

|

| Input leakage spec changed to 25 nA max | |

|

|

|

| Under AC Char, Frequency accuracy of ILO corrected | |

|

|

|

| GPIO rise time for ports 0,1 and ports 2,3 made common | |

|

|

|

| AC Programming specifications updated | |

|

|

|

| Included AC Programming cycle timing diagram | |

|

|

|

| AC SPI specification updated | |

|

|

|

| Spec change for | |

|

|

|

| Input Leakage Current maximum value changed to 1 uA | |

|

|

|

| Maximum specification for VOH5A parameter changed from 2.0 to 2.1V | |

|

|

|

| Minimum voltages for FSPIM and FSPIS specifications changed from 1.8V to 1.71V | |

|

|

|

| (Table 18) | |

|

|

|

| Updated VOHV parameter in Table 13 | |

|

|

|

| Updated Thermal impedance values for the packages - Table 20. | |

|

|

|

| Update Development Tools, add Designing with PSoC Designer. Edit, fix links and | |

|

|

|

| table format. Update TMs. Update maximum data in Table 12. DC POR and LVD | |

|

|

|

| Specifications. | |

Document Number: | Page 29 of 30 | ||||

[+] Feedback