Sheets Semi-cassette Sheet manual slot Sheet Face-Down

Series Model CLP-300 B/W 16 ppm, Color 4 ppm, SPL-C

Version no

Contents

How to use EDC Engine Diagnostic Control Mode

Information Related in Disassembly and Assembly

Block diagram

Reference Information

Safety Warning

Precautions

Toxic material

Electric Shock and Fire Safety Precautions

Assembly / Disassembly Precautions

Handling Precautions

When you move the printer

Be careful with the high temperature part

Ensure the printer is installed safely

Disregarding this warning may cause bodily injury

Super Capacitor or Lithium Battery Precautions

ESD Precautions

Product Overview

Product Specifications

General Specifications

Specifications

Controller & S/W

Paper Handling

Consumables

Environment Options Accessory

Model Comparison Table

Main Parts of System

System Structure

LSULaser Scan Unit

Cassette

Fuser Ass

ITBIntermediate Transfer Belt & 1st Transfer Roller

Structure of EP Process

EP Process

Charging

System Outline Paper path

Developing

Exposing

Transfer

Roll system

Fusing

Main Controller PBA

Main PBA Description

Main PBA

CHORUSm

Main PBA Description

Channels ADC Control Unit 2 Channels DAC Control Unit

CHORUSm Internal Block Diagram

Flash Memory Block

System Memory Block

USB2.0 Device Block

Network Block

PWM Control

Clutches Control

ADC Control

DAC Control

DC Output

SMPSSwitching Mode Power Supply PBA

AC Output

Fuser UnitHeat Lamp, Thermostat

HVPSHigh Voltage Power Supply PBA

Charger Voltage Charger

T2 Cleaning Voltage Clean T2

1st Transfer High Voltage T1+

2nd Transfer High Voltage T2+

Crum

Case of Refill Toner Install

Process after CRU life expiration

Crum Position

Controller

General Description

Processor

Printer Language Emulations

Interfaces

Periodic Replacing Parts

Control Panel

Items

Operator Panel

Power Switch

Sensor

Crums

Language Monitor

Architecture

Status Monitor

Can start polling to get the printer status

Network Interface

Printer Driver Status Monitor

LPEC2

System F/W Flow

Error status

Alarm Shortage

Crum Overview

FW Upgrade

Crum stores the following information

Initailize Flow

Samsung Electronics

Parts for Maintenance and Repair

Precautions When Replacing Parts page5-2

Information Related in Disassembly and Assembly page5-5

Disassembly Procedure page5-10

Precautions when assembling and disassembling

Precautions when replacing parts

Preautions when handling PBA

Releasing Plastic Latches

Replacement interval for parts with a limited life

Parts for Maintenance and Repair

Items Pages Printed Part number

Printer Cleaning

Special service parts

Information Related to Disassembly and Assembly

Screws used in the printer

Samsung Electronics

Disassembly and Reassembly

Samsung Electronics

Cover Unit

Disassembly Procedure

Top Cover

Remove the Left Cover

Fuser Ass’y

LSULaser Scan Unit

HVPSHigh Voltage Power Supply

Main Board

SMPSSwitching Mode Power Supply

Drive Ass’y

Follow through in Cover Unit Remove the Smps Disassembly

Transfer Roller

Open Rear Cover

Architecture

Overview

Data and Control Flow

KEY Function

Function

LED Function

Firmware downloads mode function

Black only key input process

Status LED

Service Error LED Operation

Toner-low Status Green/Red

CMYKLEDs

Start & end

Assert Error LED Operation

Onds and then All LEDs turn OFF for approximately 3 seconds

Clearing Paper Jams

Jam Removal

Cover will then close automatically

Close the rear cover and then open the top cover

Tips for Avoiding Paper Jams

Sample Pattern

Printing a Configuration

Printing a Demo

Alignment and Adjustmens

Samsung Electronics

Periodic Defective Image

Enterence

How to use EDC Engine Diagnostic Control Mode

Keys

EDC Map

Solenoid Test

Motor Test

3.3 LSU/ Fuser Test

Hvps Test

Error list and recovery

Maintenance

Off Message is disappeared

Alignment and Adjustmens

LED status legend LED pattern Possible Problem and Solution

Error Message

Procedure of Checking the Symptoms

Troubleshooting

See Solving General Printing Problems

Troubleshooting Checklist

Printed correctly Print a short document from a

Solving General Printing Problems

Manual

Troubleshooting

Samsung Electronics

Solving Print Quality Problems

Background scatter

Vertical repetitive

Ensure that the paper is loaded properly

Check for leaking toner. Clean the inside of the printer

Horizontal stripes

Character Voids

Common Macintosh Problems

Common Windows Problems

Common Linux Problems

Errors Accessible to the user owning the spooler daemon

Enabled even though I dont

Am trying to print a document

Landscape mode, but it prints

Dor to inform them of the issue

Interactively and see if you get error messages

Vertical Line and Band Vertical White Line

Major Problems Trouble shooting

Light Image Dark Image or black

Background 6 JAM

Troubleshooting

Paper Empty Cover Open Defective motor operation

No Power Vertical Line Getting Curved LSU Error

Exploded Views and Parts List

Main

Top Cover

Rear Cover

Front Cover

Main Driver1

Main Driver2

Main Frame1

Main Frame2

LSU Cover

Fuser Unit

ELA-UNIT OPC DEV

2114

ITB Unit

Casstte Unit

Service Parts List Model code CLP-300/XSG

BRACKET-P-DRIVE MOTORCLP-300,SECC,T1.2 SNA

Cable CLAMPDAMC-101,D7~8,L19,SCP-1,NTR SNA

SCREW-SPECIALPH,+,-,M3,L10.3,ZPCBLK,S SNA

CBF HARNESS-FUSELINK1CLP-300,WIRE Harn

BUSH-M-TR ITBCLP-300,POMAT-15CF,ID6 SNA

SOCKET-IC8P,DIP,SN,2.54MM SNA

RUBBER-BELT BLACKCLP-300,NBR,0.7T,-,22 SNA

TONER-YELLOWCLP-300,SAY-79GZ-K1,YELLOW SNA

RING-ETCID2.2,OD6.4,T3,BLK,STS304 SNA

FRAME-M-DEVE YELLOWCLP-300,ABS+GF20%,GR SNA

SEAL-WASTE BCLP-300,POLY-URETHANESHL SNA

TANK-M-WASTECLP-300,ABSTR557A,T2.0,W1 SNA

GUIDE-M-BUSH IDL ITB LCLP-300,POM M90-4 SNA

Smps

Main

Main Board1/15

Schematic Diagrams

ADDR123 DATA031

Main Board2/15

MMSD914T1

Main Board3/15

Vclk

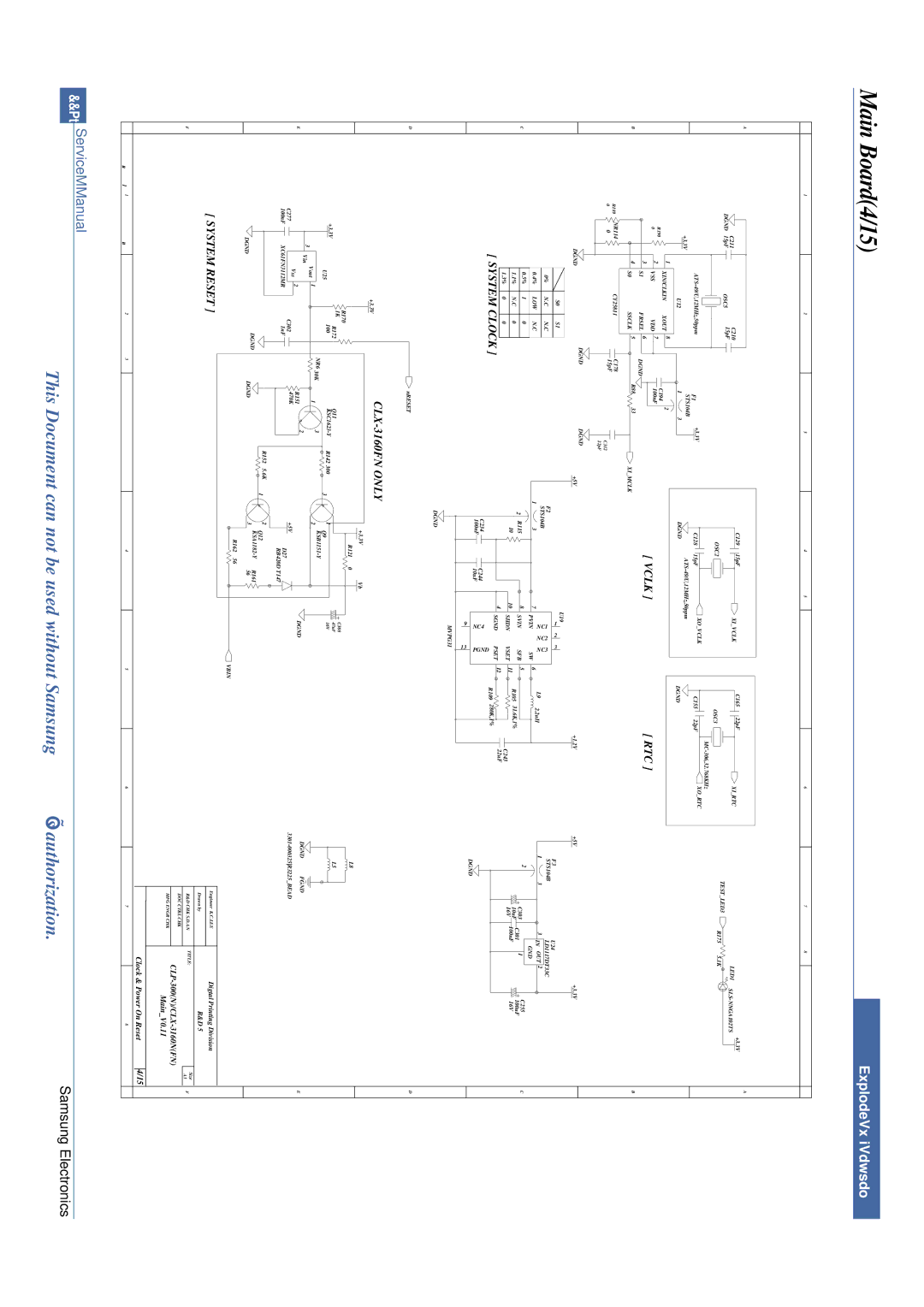

Main Board4/15

CLX-3160FN

Main Board5/15

1105-001384

Main Board6/15

CLX-3160NFN Only

Main Board7/15

CLP-300N & CLX-3160NFN Only

Main Board8/15

Main Board9/15

Invpower

For Debug

Main Board10/15

CLX-3160FN Only

Main Board11/15

Main Board12/15

Devehome

Main Board13/15

Bldc Itbclutch

Main Board14/15

Hvps

Main Board15/15

Panel

Deve INF

ITB INF

CON1 TNR01

SMPS-110V

SMPS-220V

Hvps 1/5

Hvps 2/5

Hvps 3/5

Hvps 4/5

Hvps 5/5

Tools for Troubleshooting

Acronyms and Abbreviations

Printed Board Assembly

Nonvolatile Random Access

Printer Command Language

A60, B60 Pins

Select a location for the printer

This test page is reproduced at 70% of the normal A4 size

12.4 A4 ISO 19752 Standard Pattern