ARM720T_LH79520 – Sharp LH79520 SoC with ARM720T

Architectural Overview

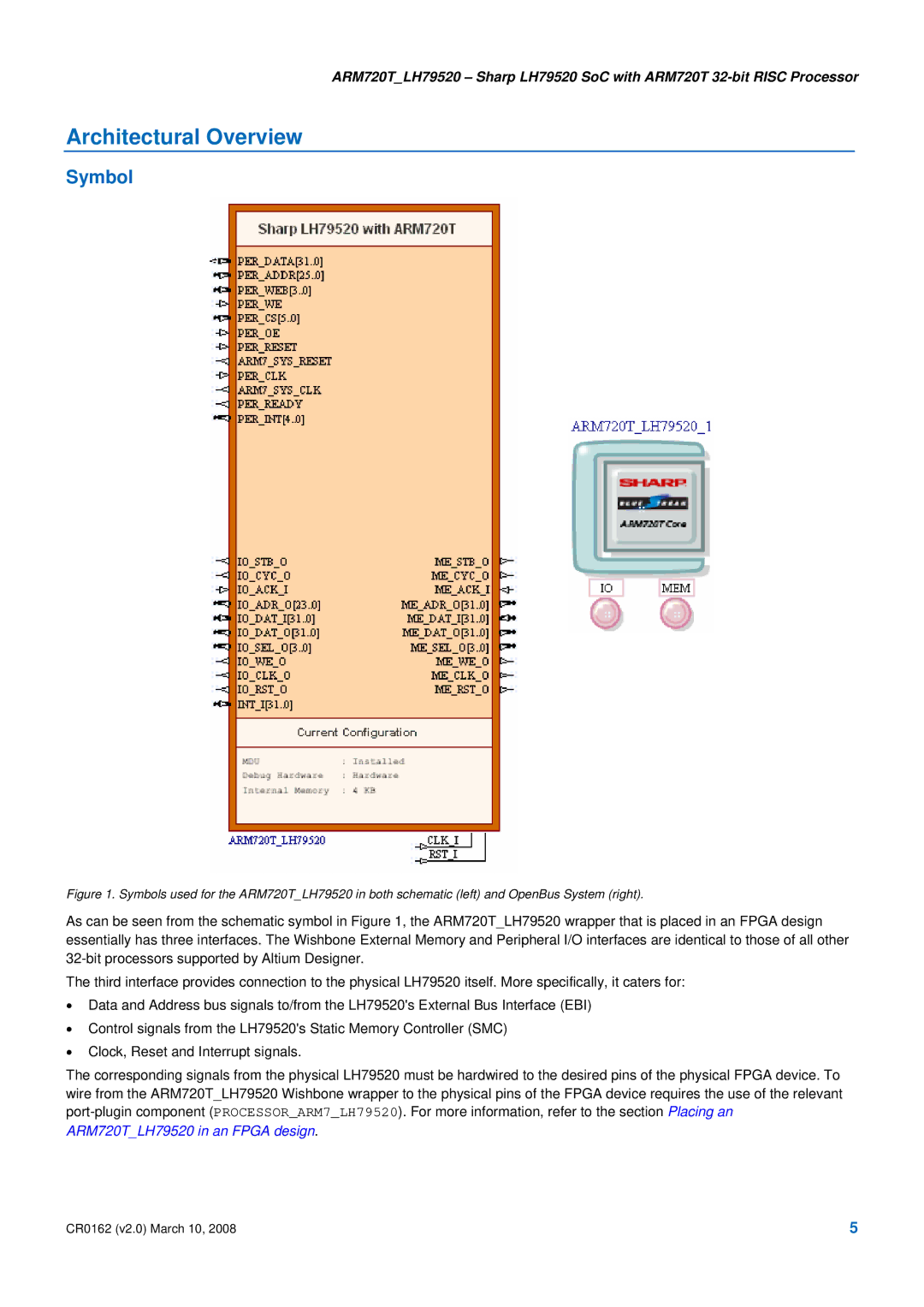

Symbol

Figure 1. Symbols used for the ARM720T_LH79520 in both schematic (left) and OpenBus System (right).

As can be seen from the schematic symbol in Figure 1, the ARM720T_LH79520 wrapper that is placed in an FPGA design essentially has three interfaces. The Wishbone External Memory and Peripheral I/O interfaces are identical to those of all other

The third interface provides connection to the physical LH79520 itself. More specifically, it caters for:

•Data and Address bus signals to/from the LH79520's External Bus Interface (EBI)

•Control signals from the LH79520's Static Memory Controller (SMC)

•Clock, Reset and Interrupt signals.

The corresponding signals from the physical LH79520 must be hardwired to the desired pins of the physical FPGA device. To wire from the ARM720T_LH79520 Wishbone wrapper to the physical pins of the FPGA device requires the use of the relevant

CR0162 (v2.0) March 10, 2008 | 5 |