ARM720T_LH79520 – Sharp LH79520 SoC with ARM720T

Name | Type | Polarity/Bus size | Description |

|

|

|

|

PER_RESET | I | Low | Reset signal from the LH79520. |

|

|

|

|

ARM7_SYS_RESE | O | Low | Reset signal to the LH79520 (internally connected from the RST_I |

T |

|

| line). |

PER_CLK | I | Rise | Clock signal from the LH79520 |

|

|

|

|

ARM7_SYS_CLK | O | Rise | External Clock signal to the LH79520 (internally connected from the |

|

|

| CLK_I line). |

PER_READY | O | Low | Static Memory Controller External Wait Control |

|

|

|

|

PER_INT | O | 5/High | External Interrupt lines. These lines appear as interrupts 0 to 4 when |

|

|

| handled by the physical device's Vectored Interrupt Controller (see |

|

|

| Interrupts). |

Configuring the Processor

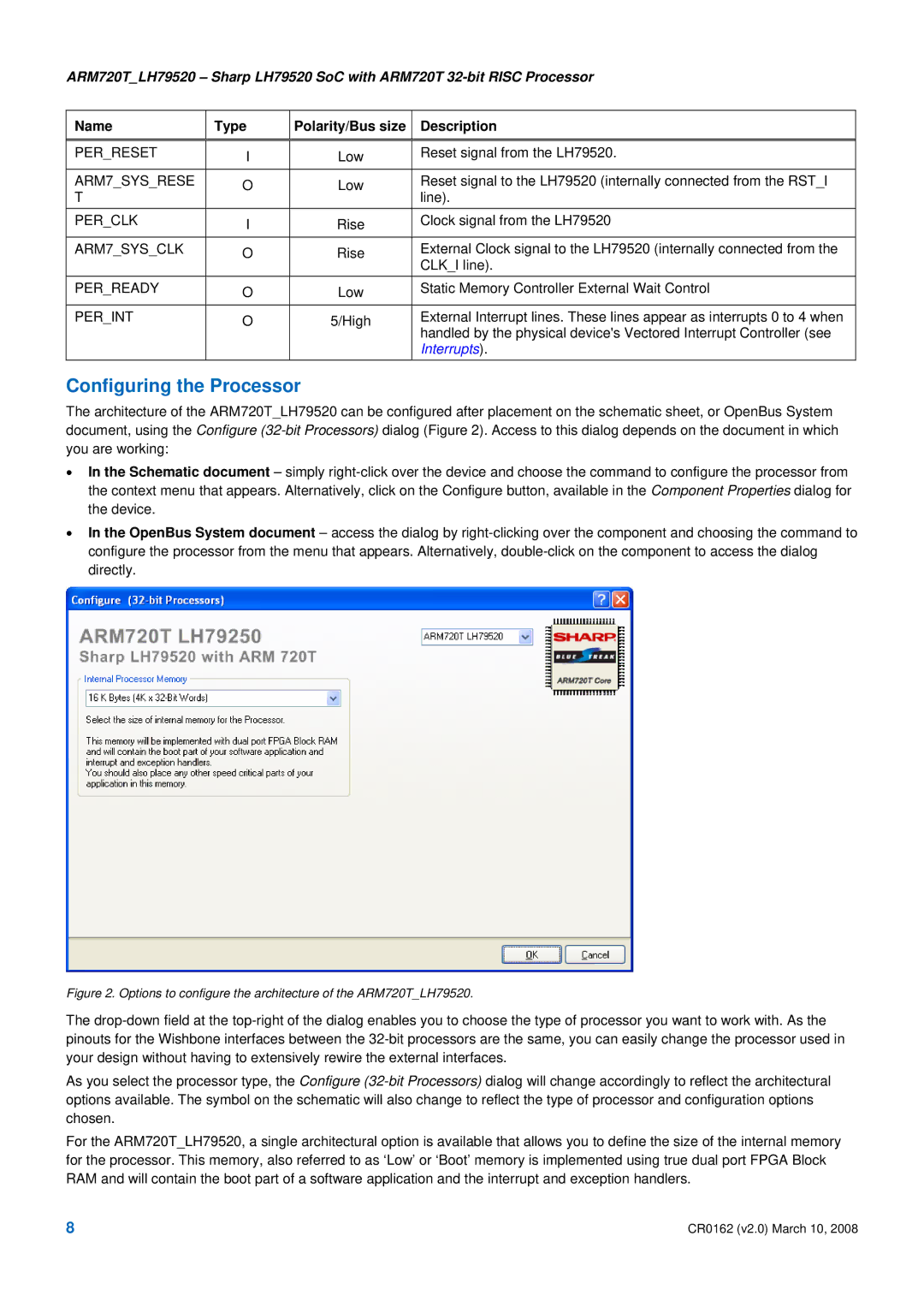

The architecture of the ARM720T_LH79520 can be configured after placement on the schematic sheet, or OpenBus System document, using the Configure

•In the Schematic document – simply

•In the OpenBus System document – access the dialog by

Figure 2. Options to configure the architecture of the ARM720T_LH79520.

The

As you select the processor type, the Configure

For the ARM720T_LH79520, a single architectural option is available that allows you to define the size of the internal memory for the processor. This memory, also referred to as ‘Low’ or ‘Boot’ memory is implemented using true dual port FPGA Block RAM and will contain the boot part of a software application and the interrupt and exception handlers.

8 | CR0162 (v2.0) March 10, 2008 |