ARM720T_LH79520 – Sharp LH79520 SoC with ARM720T

clock signal (CLK_I), an acknowledge signal fails to appear from the addressed slave peripheral device, the wait request to the ARM720T is dropped, the processor times out normally and the current data transfer cycle is forcibly terminated.

The ACK_O signal from a slave peripheral should not be used as a ‘long delay’

For more information on connection of slave physical memory and peripheral I/O devices to the processor's Wishbone interfaces, refer to the application note Connecting Memory and Peripheral Devices to a

Data Organization

Data organization refers to the ordering of the data during transfers. There are two general types of ordering:

•BIG ENDIAN – the most significant portion of an operand is stored at the lower address

•LITTLE ENDIAN – the most significant portion of an operand is stored at the higher address.

The ARM720T_LH79520 supports both of these, but is left in its default Little Endian mode after a reset. To use Big Endian data, you would need to configure the processor accordingly. Refer to the ARM720T Technical Reference Manual for further information.

Words, Half-Words and Bytes

The ARM720T_LH79520 operates on the following data sizes:

•

•

•

There are dedicated load and store instructions for these three data types.

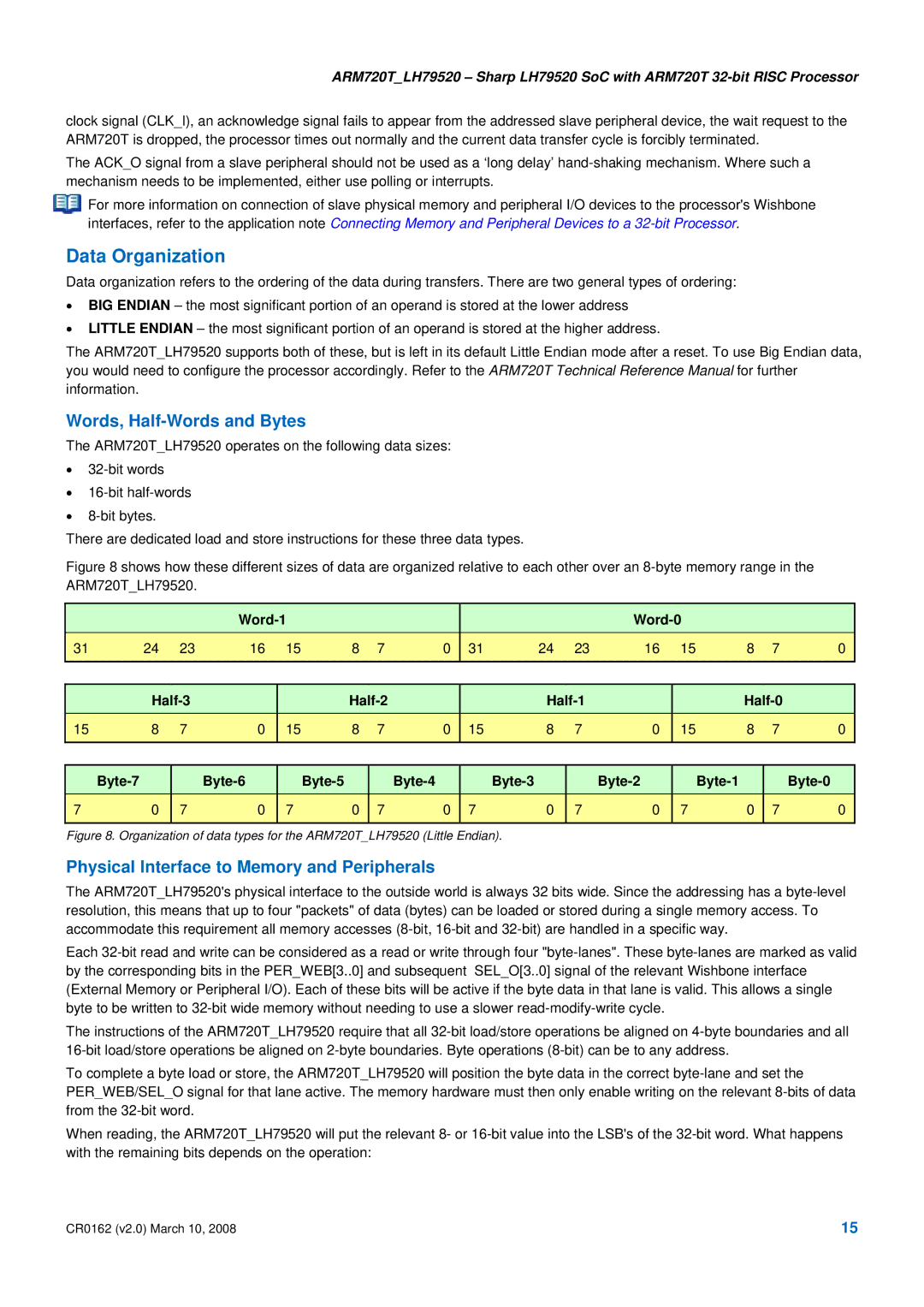

Figure 8 shows how these different sizes of data are organized relative to each other over an 8-byte memory range in the ARM720T_LH79520.

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

31 | 24 | 23 | 16 | 15 | 8 | 7 | 0 | 31 | 24 |

|

| 23 | 16 |

| 15 | 8 | 7 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| ||||||||||

15 | 8 | 7 | 0 | 15 | 8 | 7 | 0 | 15 | 8 |

|

| 7 | 0 |

| 15 | 8 | 7 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

7 | 0 | 7 | 0 | 7 | 0 | 7 | 0 | 7 | 0 |

| 7 | 0 |

| 7 | 0 | 7 | 0 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 8. Organization of data types for the ARM720T_LH79520 (Little Endian).

Physical Interface to Memory and Peripherals

The ARM720T_LH79520's physical interface to the outside world is always 32 bits wide. Since the addressing has a

Each

The instructions of the ARM720T_LH79520 require that all

To complete a byte load or store, the ARM720T_LH79520 will position the byte data in the correct

PER_WEB/SEL_O signal for that lane active. The memory hardware must then only enable writing on the relevant

When reading, the ARM720T_LH79520 will put the relevant 8- or

CR0162 (v2.0) March 10, 2008 | 15 |