ARM720T_LH79520 – Sharp LH79520 SoC with ARM720T

Memory & I/O Management

The ARM720T_LH79520 uses

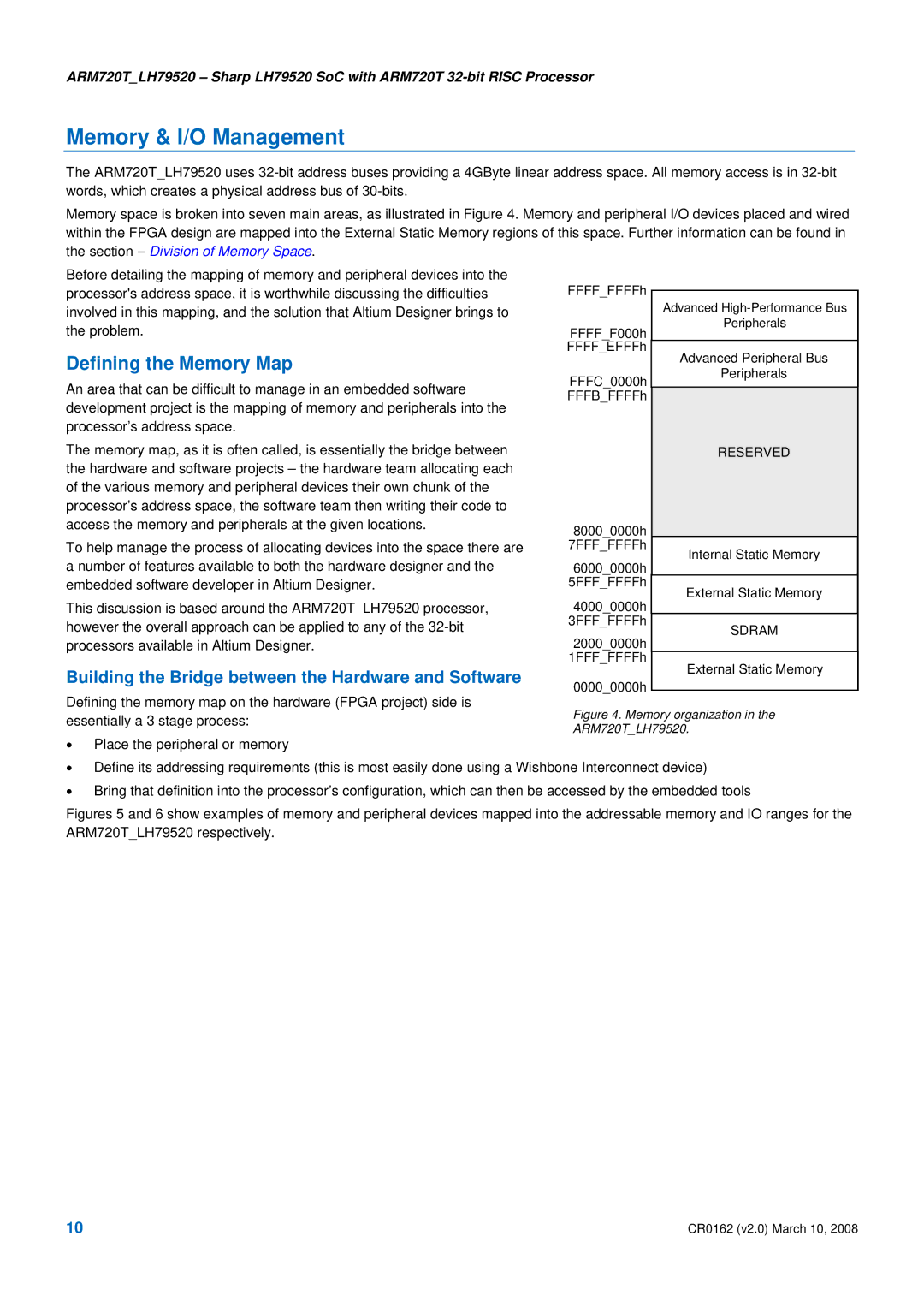

Memory space is broken into seven main areas, as illustrated in Figure 4. Memory and peripheral I/O devices placed and wired within the FPGA design are mapped into the External Static Memory regions of this space. Further information can be found in the section – Division of Memory Space.

Before detailing the mapping of memory and peripheral devices into the processor's address space, it is worthwhile discussing the difficulties involved in this mapping, and the solution that Altium Designer brings to the problem.

Defining the Memory Map

An area that can be difficult to manage in an embedded software development project is the mapping of memory and peripherals into the processor’s address space.

The memory map, as it is often called, is essentially the bridge between the hardware and software projects – the hardware team allocating each of the various memory and peripheral devices their own chunk of the processor’s address space, the software team then writing their code to access the memory and peripherals at the given locations.

To help manage the process of allocating devices into the space there are a number of features available to both the hardware designer and the embedded software developer in Altium Designer.

This discussion is based around the ARM720T_LH79520 processor, however the overall approach can be applied to any of the

Building the Bridge between the Hardware and Software

FFFF_FFFFh

FFFF_F000h FFFF_EFFFh

FFFC_0000h FFFB_FFFFh

8000_0000h 7FFF_FFFFh

6000_0000h 5FFF_FFFFh

4000_0000h 3FFF_FFFFh

2000_0000h 1FFF_FFFFh

0000_0000h

Advanced

Peripherals

Advanced Peripheral Bus

Peripherals

RESERVED

Internal Static Memory

External Static Memory

SDRAM

External Static Memory

Defining the memory map on the hardware (FPGA project) side is essentially a 3 stage process:

•Place the peripheral or memory

Figure 4. Memory organization in the ARM720T_LH79520.

•Define its addressing requirements (this is most easily done using a Wishbone Interconnect device)

•Bring that definition into the processor’s configuration, which can then be accessed by the embedded tools

Figures 5 and 6 show examples of memory and peripheral devices mapped into the addressable memory and IO ranges for the ARM720T_LH79520 respectively.

10 | CR0162 (v2.0) March 10, 2008 |