THEORY OF OPERATION

CN3

DATA 1

DATA 2

DARA 3

DATA 4

DATA 5

DARA 6

DATA 7

DATA 8

STROBE

BUSY

ACK

ERROR

SELECTED

PAPER OUT

CN1 | CN9 |

| IC10 | ||

A4 | A4 |

| CD0 | ||

|

|

| |||

B4 | B4 |

| CD1 | ||

|

|

| |||

A5 | A5 |

| CD2 | ||

|

|

| |||

B5 | B5 |

| CD3 | ||

|

|

| |||

A6 | A6 |

| CD4 | ||

|

|

| |||

B6 | B6 |

| CD5 | ||

|

|

| |||

A7 | A7 |

| CD6 | ||

|

|

| |||

B7 | B7 |

| CD7 | ||

|

|

| |||

A13 | A13 |

| CSTB | ||

|

|

| |||

A12 | A12 |

|

|

|

|

| BUSY | ||||

|

|

| |||

B12 | B12 |

| ACK | ||

|

|

| |||

A10 | A10 |

| ERROR | ||

|

|

| |||

A11 | A11 |

|

|

|

|

| SELECT | ||||

|

|

| |||

B11 | B11 |

|

|

|

|

| POUT | ||||

|

|

| |||

|

|

| Gate array | ||

IC5

CPU

LS05

IC1

Parallel Interface PCB | Main PCB |

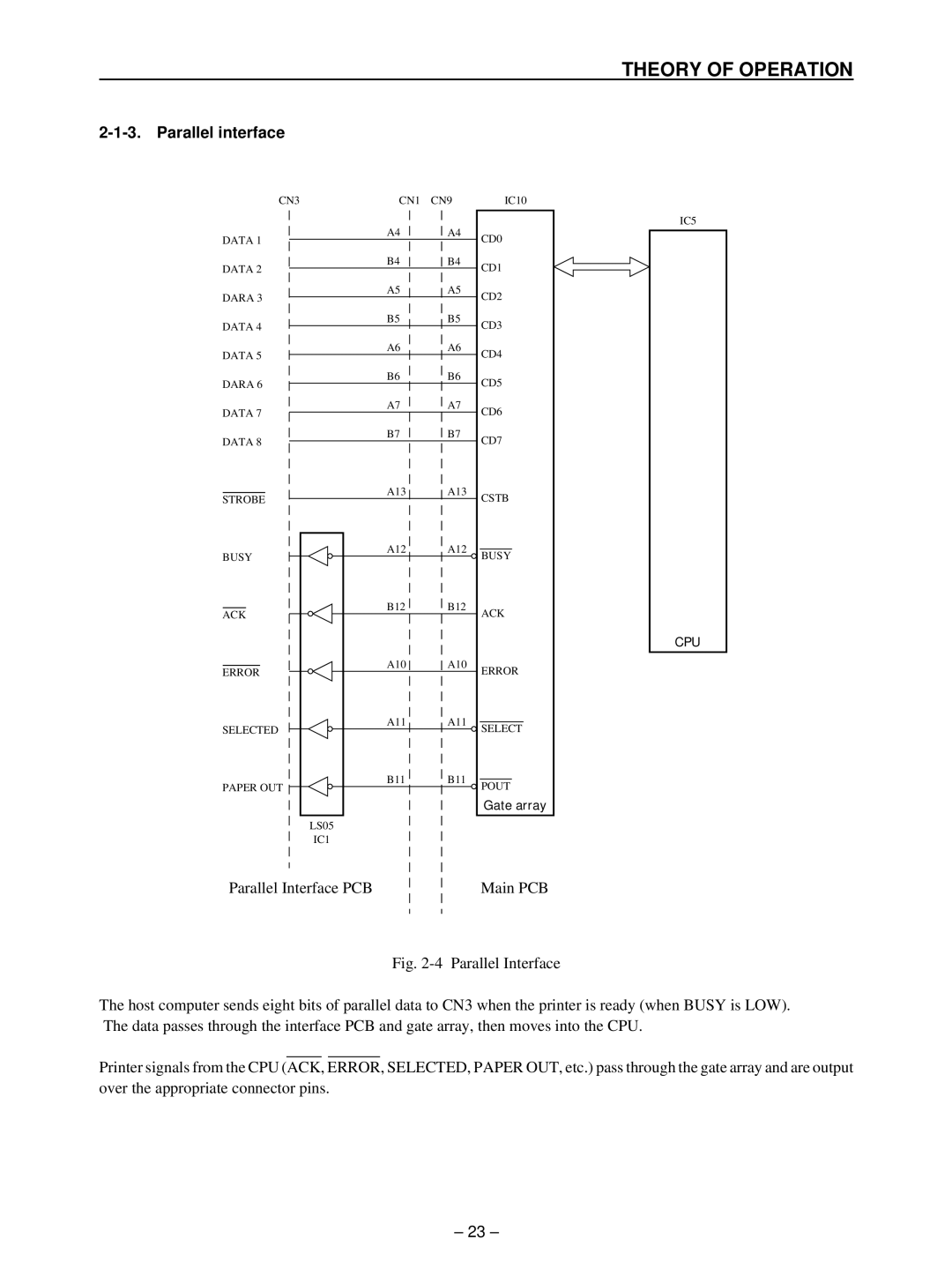

Fig. 2-4 Parallel Interface

The host computer sends eight bits of parallel data to CN3 when the printer is ready (when BUSY is LOW). The data passes through the interface PCB and gate array, then moves into the CPU.

Printer signals from the CPU (ACK, ERROR, SELECTED, PAPER OUT, etc.) pass through the gate array and are output over the appropriate connector pins.

– 23 –