Registers

5.5Clear Data Register (CLR_DATA)

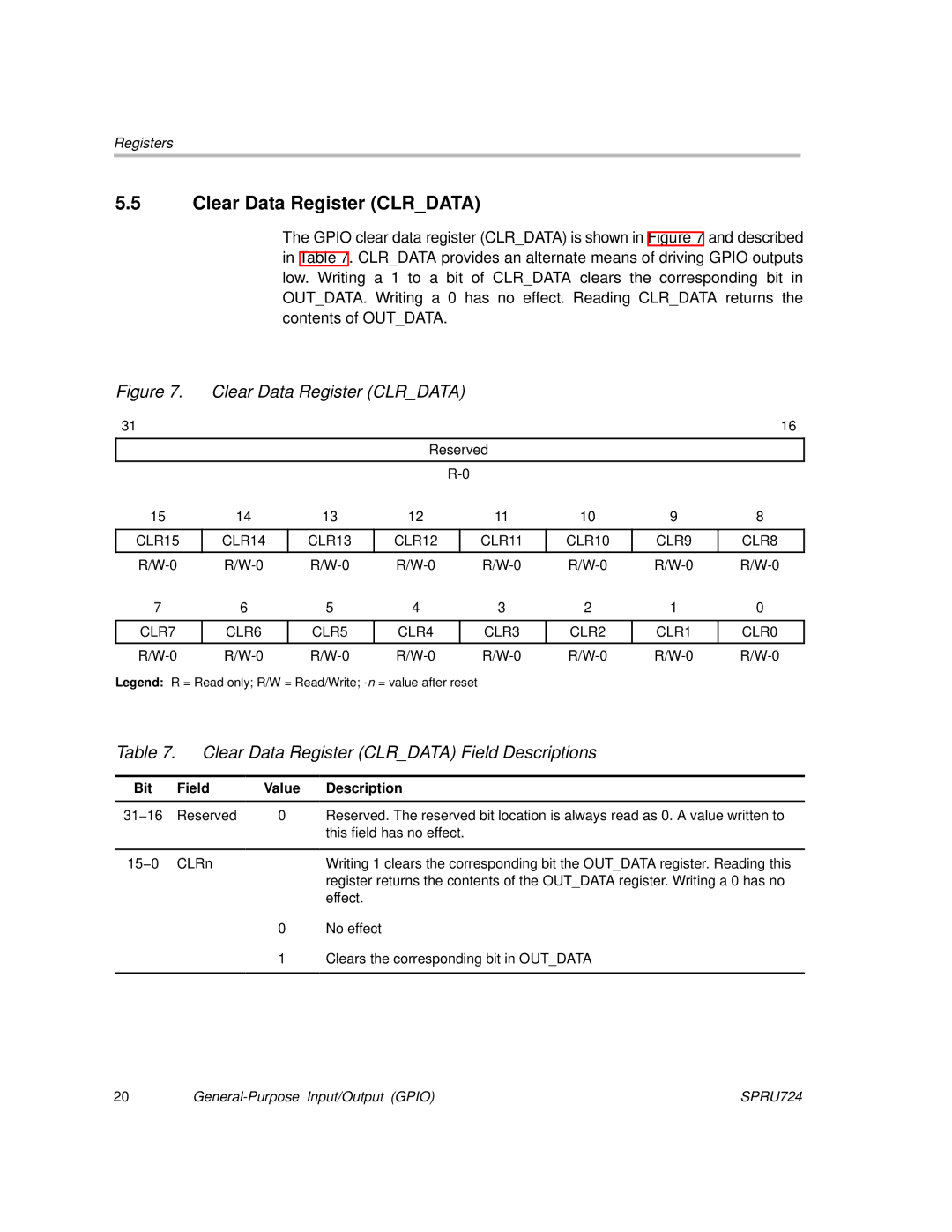

The GPIO clear data register (CLR_DATA) is shown in Figure 7 and described in Table 7. CLR_DATA provides an alternate means of driving GPIO outputs low. Writing a 1 to a bit of CLR_DATA clears the corresponding bit in OUT_DATA. Writing a 0 has no effect. Reading CLR_DATA returns the contents of OUT_DATA.

Figure 7. | Clear Data Register (CLR_DATA) |

|

|

|

| |||

31 |

|

|

|

|

|

|

| 16 |

|

|

|

|

|

|

|

| |

|

|

| Reserved |

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

15 | 14 | 13 | 12 |

| 11 | 10 | 9 | 8 |

|

|

|

|

|

|

|

|

|

CLR15 | CLR14 | CLR13 | CLR12 |

| CLR11 | CLR10 | CLR9 | CLR8 |

|

|

|

|

|

|

|

|

|

7 | 6 | 5 | 4 |

| 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

| |

CLR7 | CLR6 | CLR5 | CLR4 |

| CLR3 | CLR2 | CLR1 | CLR0 |

|

|

|

|

|

|

|

|

|

Legend: R = Read only; R/W = Read/Write; |

|

|

|

| ||||

Table 7. | Clear Data Register (CLR_DATA) Field Descriptions | ||

|

|

|

|

Bit | Field | Value | Description |

|

|

|

|

31−16 | Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to |

|

|

| this field has no effect. |

|

|

|

|

15−0 | CLRn |

| Writing 1 clears the corresponding bit the OUT_DATA register. Reading this |

|

|

| register returns the contents of the OUT_DATA register. Writing a 0 has no |

|

|

| effect. |

|

|

|

|

|

| 0 | No effect |

|

|

|

|

|

| 1 | Clears the corresponding bit in OUT_DATA |

|

|

|

|

20 | SPRU724 |