Interrupt and Event Generation

3 Interrupt and Event Generation

Each GPIO pin (GPn) can be configured to generate a CPU interrupt (GPINTn) and a synchronization event to the EDMA controller (GPINTn). The interrupt and EDMA event can be generated on the

The direction of the GPIO pin does not need to be input when using the pin to generate the interrupt and EDMA event. When the GPIO pin is configured as input, transitions on the pin trigger interrupts and EDMA events. When the GPIO pin is configured as output, software can toggle the GPIO output register to change the pin state and in turn trigger the interrupt and EDMA event.

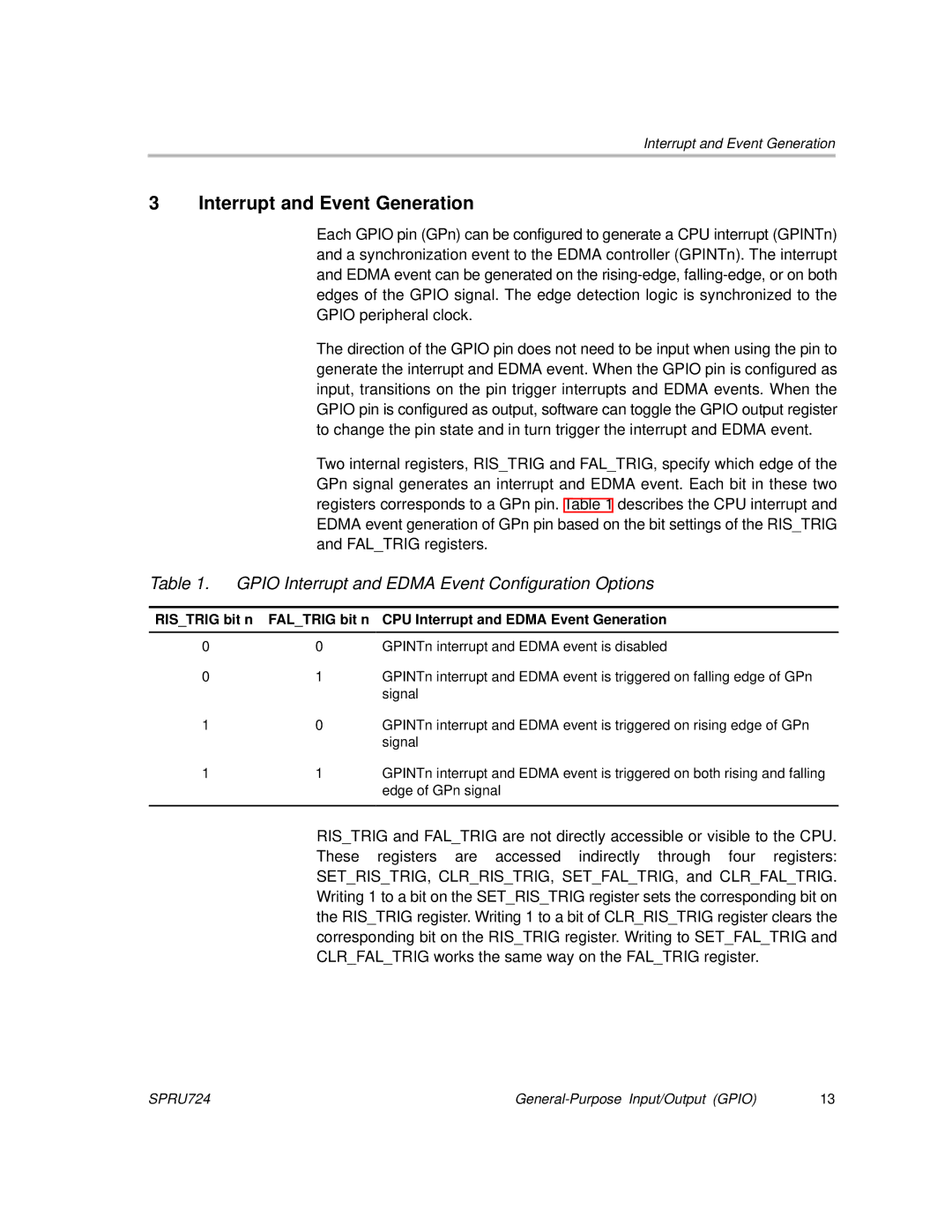

Two internal registers, RIS_TRIG and FAL_TRIG, specify which edge of the GPn signal generates an interrupt and EDMA event. Each bit in these two registers corresponds to a GPn pin. Table 1 describes the CPU interrupt and EDMA event generation of GPn pin based on the bit settings of the RIS_TRIG and FAL_TRIG registers.

Table 1. GPIO Interrupt and EDMA Event Configuration Options

RIS_TRIG bit n | FAL_TRIG bit n CPU Interrupt and EDMA Event Generation | |

0 | 0 | GPINTn interrupt and EDMA event is disabled |

0 | 1 | GPINTn interrupt and EDMA event is triggered on falling edge of GPn |

|

| signal |

1 | 0 | GPINTn interrupt and EDMA event is triggered on rising edge of GPn |

|

| signal |

1 | 1 | GPINTn interrupt and EDMA event is triggered on both rising and falling |

|

| edge of GPn signal |

|

|

|

RIS_TRIG and FAL_TRIG are not directly accessible or visible to the CPU. These registers are accessed indirectly through four registers: SET_RIS_TRIG, CLR_RIS_TRIG, SET_FAL_TRIG, and CLR_FAL_TRIG. Writing 1 to a bit on the SET_RIS_TRIG register sets the corresponding bit on the RIS_TRIG register. Writing 1 to a bit of CLR_RIS_TRIG register clears the corresponding bit on the RIS_TRIG register. Writing to SET_FAL_TRIG and CLR_FAL_TRIG works the same way on the FAL_TRIG register.

SPRU724 | 13 |