Registers

5.1Interrupt Per-Bank Enable Register (BINTEN)

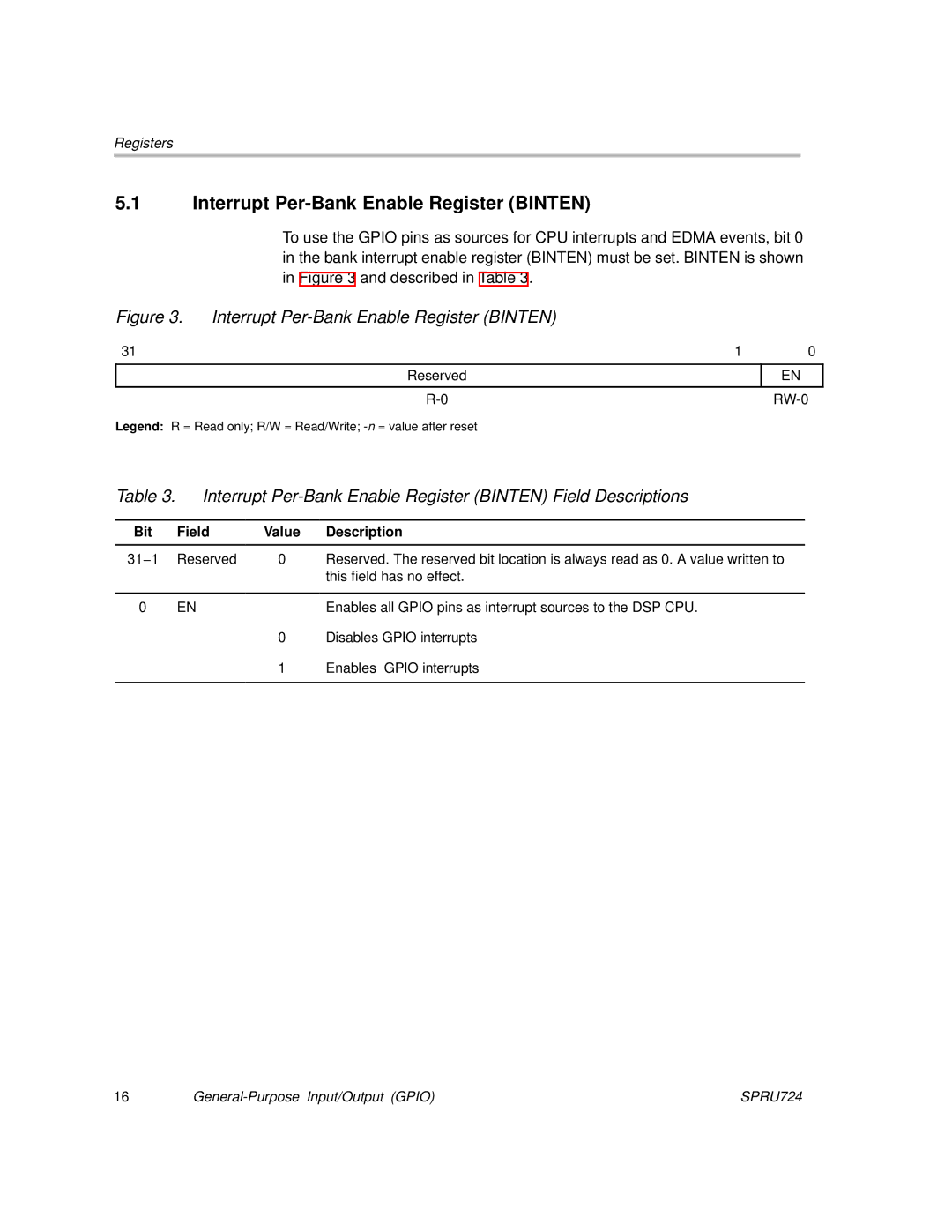

To use the GPIO pins as sources for CPU interrupts and EDMA events, bit 0 in the bank interrupt enable register (BINTEN) must be set. BINTEN is shown in Figure 3 and described in Table 3.

Figure 3. | Interrupt |

|

|

31 |

| 1 | 0 |

|

|

|

|

| Reserved |

| EN |

|

|

|

|

|

| ||

Legend: R = Read only; R/W = Read/Write; |

|

| |

Table 3. | Interrupt | ||

|

|

|

|

Bit | Field | Value | Description |

|

|

|

|

31−1 | Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to |

|

|

| this field has no effect. |

|

|

|

|

0 | EN |

| Enables all GPIO pins as interrupt sources to the DSP CPU. |

|

| 0 | Disables GPIO interrupts |

|

| 1 | Enables GPIO interrupts |

|

|

|

|

16 | SPRU724 |