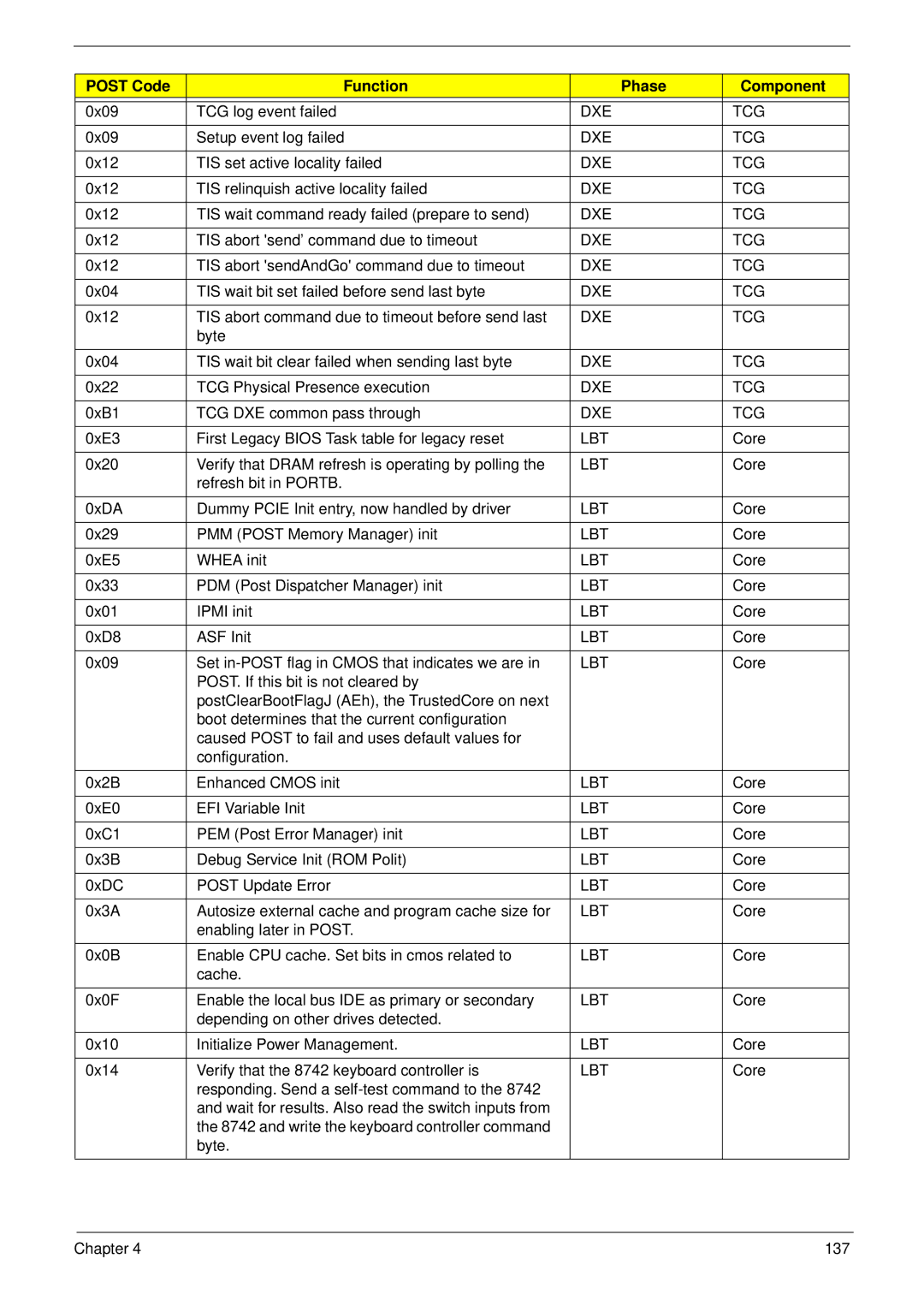

POST Code | Function | Phase | Component |

|

|

|

|

0x09 | TCG log event failed | DXE | TCG |

0x09 | Setup event log failed | DXE | TCG |

|

|

|

|

0x12 | TIS set active locality failed | DXE | TCG |

|

|

|

|

0x12 | TIS relinquish active locality failed | DXE | TCG |

|

|

|

|

0x12 | TIS wait command ready failed (prepare to send) | DXE | TCG |

|

|

|

|

0x12 | TIS abort 'send’ command due to timeout | DXE | TCG |

|

|

|

|

0x12 | TIS abort 'sendAndGo' command due to timeout | DXE | TCG |

|

|

|

|

0x04 | TIS wait bit set failed before send last byte | DXE | TCG |

|

|

|

|

0x12 | TIS abort command due to timeout before send last | DXE | TCG |

| byte |

|

|

|

|

|

|

0x04 | TIS wait bit clear failed when sending last byte | DXE | TCG |

|

|

|

|

0x22 | TCG Physical Presence execution | DXE | TCG |

|

|

|

|

0xB1 | TCG DXE common pass through | DXE | TCG |

|

|

|

|

0xE3 | First Legacy BIOS Task table for legacy reset | LBT | Core |

|

|

|

|

0x20 | Verify that DRAM refresh is operating by polling the | LBT | Core |

| refresh bit in PORTB. |

|

|

|

|

|

|

0xDA | Dummy PCIE Init entry, now handled by driver | LBT | Core |

|

|

|

|

0x29 | PMM (POST Memory Manager) init | LBT | Core |

|

|

|

|

0xE5 | WHEA init | LBT | Core |

|

|

|

|

0x33 | PDM (Post Dispatcher Manager) init | LBT | Core |

|

|

|

|

0x01 | IPMI init | LBT | Core |

|

|

|

|

0xD8 | ASF Init | LBT | Core |

|

|

|

|

0x09 | Set | LBT | Core |

| POST. If this bit is not cleared by |

|

|

| postClearBootFlagJ (AEh), the TrustedCore on next |

|

|

| boot determines that the current configuration |

|

|

| caused POST to fail and uses default values for |

|

|

| configuration. |

|

|

|

|

|

|

0x2B | Enhanced CMOS init | LBT | Core |

|

|

|

|

0xE0 | EFI Variable Init | LBT | Core |

|

|

|

|

0xC1 | PEM (Post Error Manager) init | LBT | Core |

|

|

|

|

0x3B | Debug Service Init (ROM Polit) | LBT | Core |

|

|

|

|

0xDC | POST Update Error | LBT | Core |

|

|

|

|

0x3A | Autosize external cache and program cache size for | LBT | Core |

| enabling later in POST. |

|

|

|

|

|

|

0x0B | Enable CPU cache. Set bits in cmos related to | LBT | Core |

| cache. |

|

|

|

|

|

|

0x0F | Enable the local bus IDE as primary or secondary | LBT | Core |

| depending on other drives detected. |

|

|

|

|

|

|

0x10 | Initialize Power Management. | LBT | Core |

|

|

|

|

0x14 | Verify that the 8742 keyboard controller is | LBT | Core |

| responding. Send a |

|

|

| and wait for results. Also read the switch inputs from |

|

|

| the 8742 and write the keyboard controller command |

|

|

| byte. |

|

|

|

|

|

|

Chapter 4 | 137 |