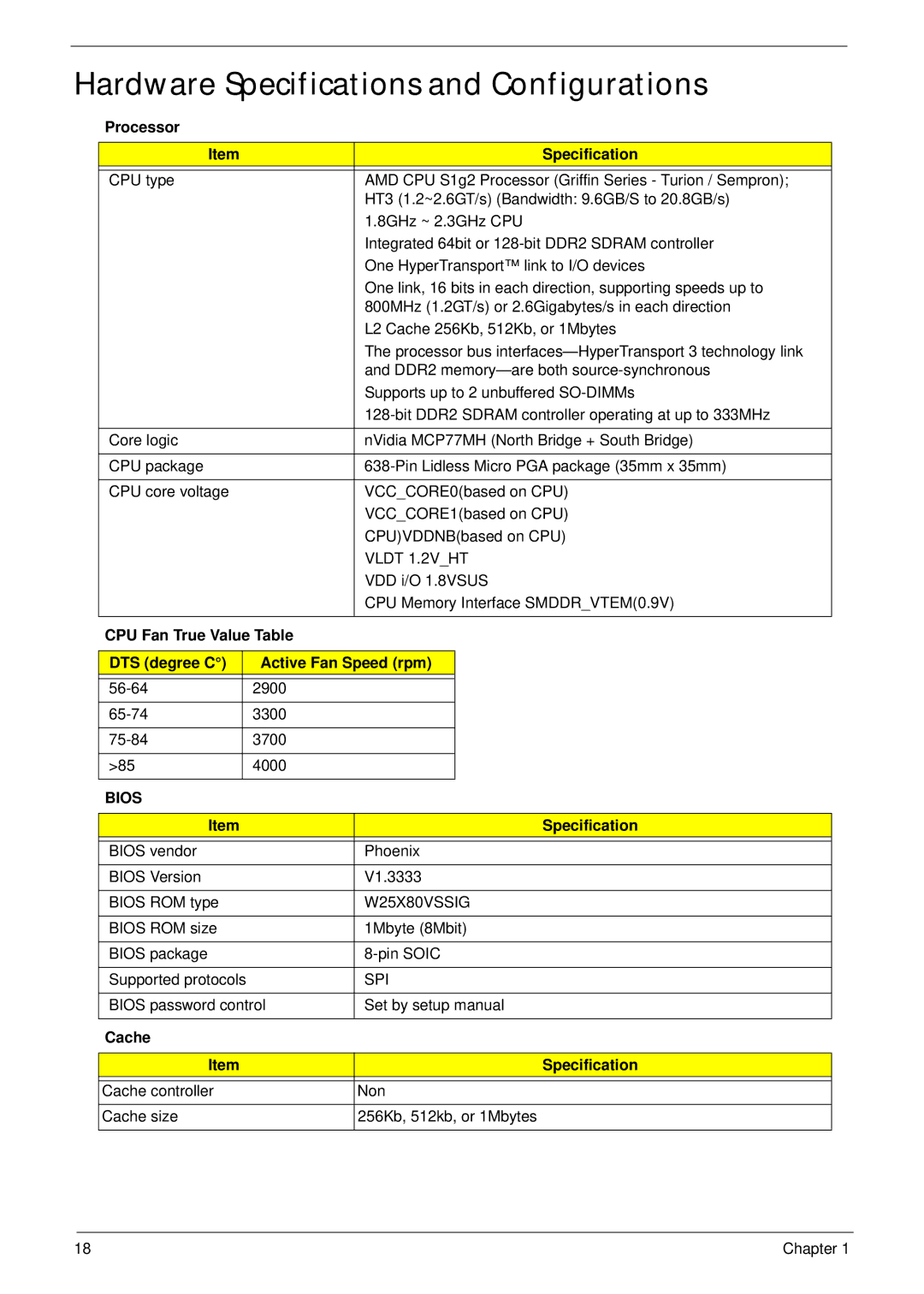

Hardware Specifications and Configurations

Processor

Item |

|

| Specification | |

|

|

|

|

|

CPU type |

| AMD CPU S1g2 Processor (Griffin Series - Turion / Sempron); | ||

|

|

| HT3 (1.2~2.6GT/s) (Bandwidth: 9.6GB/S to 20.8GB/s) | |

|

|

| 1.8GHz ~ 2.3GHz CPU | |

|

|

| Integrated 64bit or | |

|

|

| One HyperTransport™ link to I/O devices | |

|

|

| One link, 16 bits in each direction, supporting speeds up to | |

|

|

| 800MHz (1.2GT/s) or 2.6Gigabytes/s in each direction | |

|

|

| L2 Cache 256Kb, 512Kb, or 1Mbytes | |

|

|

| The processor bus | |

|

|

| and DDR2 | |

|

|

| Supports up to 2 unbuffered | |

|

|

| ||

|

|

|

|

|

Core logic |

| nVidia MCP77MH (North Bridge + South Bridge) | ||

|

|

|

|

|

CPU package |

| |||

|

|

|

|

|

CPU core voltage |

| VCC_CORE0(based on CPU) | ||

|

|

| VCC_CORE1(based on CPU) | |

|

|

| CPU)VDDNB(based on CPU) | |

|

|

| VLDT 1.2V_HT | |

|

|

| VDD i/O 1.8VSUS | |

|

|

| CPU Memory Interface SMDDR_VTEM(0.9V) | |

|

|

|

| |

CPU Fan True Value Table |

|

| ||

|

|

|

|

|

DTS (degree C°) |

| Active Fan Speed (rpm) |

| |

|

|

|

|

|

| 2900 |

|

| |

|

|

|

|

|

| 3300 |

|

| |

|

|

|

|

|

| 3700 |

|

| |

|

|

|

|

|

>85 |

| 4000 |

|

|

|

|

|

|

|

BIOS |

|

|

| |

|

|

|

|

|

Item |

|

| Specification | |

|

|

| ||

BIOS vendor |

| Phoenix | ||

BIOS Version |

| V1.3333 | ||

|

|

| ||

BIOS ROM type |

| W25X80VSSIG | ||

|

|

| ||

BIOS ROM size |

| 1Mbyte (8Mbit) | ||

|

|

| ||

BIOS package |

| |||

|

|

| ||

Supported protocols |

| SPI | ||

|

| |||

BIOS password control | Set by setup manual | |||

|

|

|

| |

Cache |

|

|

| |

|

|

|

|

|

Item |

|

| Specification | |

|

|

| ||

Cache controller |

| Non | ||

|

|

| ||

Cache size |

| 256Kb, 512kb, or 1Mbytes | ||

|

|

|

|

|

18 | Chapter 1 |