ADSP-21020

ENVIRONMENTAL CONDITIONS

The

The commercial grade (K grade)

operation at TAMB of 0°C to +70°C. Maximum TCASE (case temperature) can be calculated from the following equation:

TCASE = T AMB + (PD × θCA )

where PD is power dissipation and θCA is the

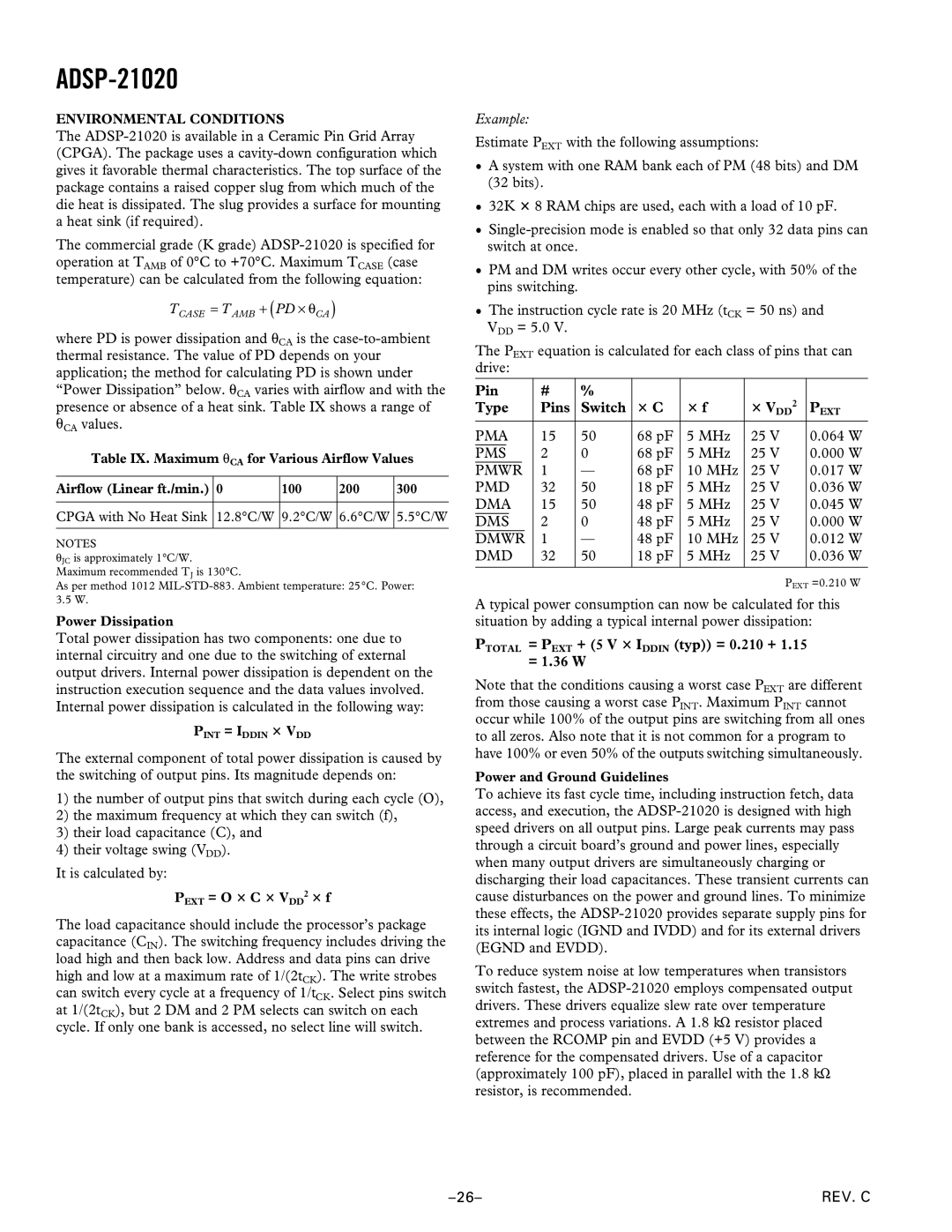

Table IX. Maximum θCA for Various Airflow Values

Airflow (Linear ft./min.) | 0 | 100 | 200 | 300 |

|

|

|

|

|

CPGA with No Heat Sink | 12.8°C/W | 9.2°C/W | 6.6°C/W | 5.5°C/W |

|

|

|

|

|

NOTES |

|

|

| |

θJC is approximately 1°C/W. |

|

|

| |

Maximum recommended TJ is 130°C. |

|

|

| |

As per method 1012

Power Dissipation

Total power dissipation has two components: one due to internal circuitry and one due to the switching of external output drivers. Internal power dissipation is dependent on the instruction execution sequence and the data values involved. Internal power dissipation is calculated in the following way:

PINT = IDDIN 3 VDD

The external component of total power dissipation is caused by the switching of output pins. Its magnitude depends on:

1)the number of output pins that switch during each cycle (O),

2)the maximum frequency at which they can switch (f),

3)their load capacitance (C), and

4)their voltage swing (VDD).

It is calculated by:

PEXT = O 3 C 3 VDD2 3 f

The load capacitance should include the processor’s package capacitance (CIN). The switching frequency includes driving the load high and then back low. Address and data pins can drive high and low at a maximum rate of 1/(2tCK). The write strobes can switch every cycle at a frequency of 1/tCK. Select pins switch at 1/(2tCK), but 2 DM and 2 PM selects can switch on each cycle. If only one bank is accessed, no select line will switch.

Example:

Estimate PEXT with the following assumptions:

•A system with one RAM bank each of PM (48 bits) and DM (32 bits).

•32K 3 8 RAM chips are used, each with a load of 10 pF.

•

•PM and DM writes occur every other cycle, with 50% of the pins switching.

•The instruction cycle rate is 20 MHz (tCK = 50 ns) and VDD = 5.0 V.

The PEXT equation is calculated for each class of pins that can drive:

Pin | # | % |

|

| 3 VDD2 |

| |||

Type | Pins | Switch | 3 C | 3 f | PEXT | ||||

PMA | 15 | 50 | 68 pF | 5 MHz | 25 V | 0.064 W | |||

PMS | 2 | 0 | 68 pF | 5 MHz | 25 V | 0.000 W | |||

PMWR |

|

| 1 | — | 68 pF | 10 MHz | 25 V | 0.017 W | |

PMD | 32 | 50 | 18 pF | 5 MHz | 25 V | 0.036 W | |||

DMA | 15 | 50 | 48 pF | 5 MHz | 25 V | 0.045 W | |||

DMS |

|

| 2 | 0 | 48 pF | 5 MHz | 25 V | 0.000 W | |

DMWR |

| 1 | — | 48 pF | 10 MHz | 25 V | 0.012 W | ||

DMD | 32 | 50 | 18 pF | 5 MHz | 25 V | 0.036 W | |||

|

|

|

|

|

|

|

|

|

|

PEXT =0.210 W

A typical power consumption can now be calculated for this situation by adding a typical internal power dissipation:

PTOTAL = PEXT + (5 V 3 IDDIN (typ)) = 0.210 + 1.15 = 1.36 W

Note that the conditions causing a worst case PEXT are different from those causing a worst case PINT. Maximum PINT cannot occur while 100% of the output pins are switching from all ones to all zeros. Also note that it is not common for a program to have 100% or even 50% of the outputs switching simultaneously.

Power and Ground Guidelines

To achieve its fast cycle time, including instruction fetch, data access, and execution, the

To reduce system noise at low temperatures when transistors switch fastest, the

REV. C |