ADSP-21020

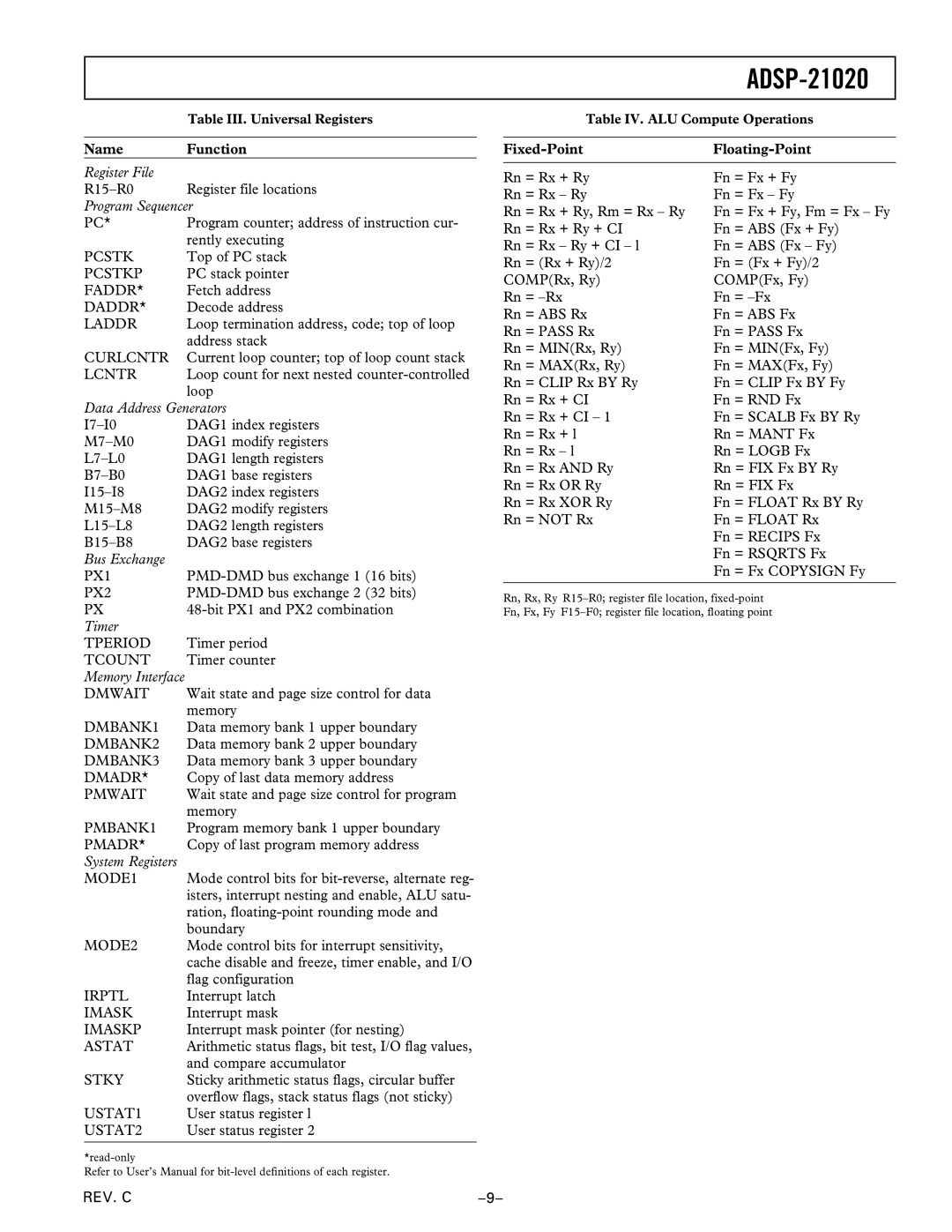

| Table III. Universal Registers |

|

|

Name | Function |

Register File |

|

Register file locations | |

Program Sequencer | |

PC* | Program counter; address of instruction cur- |

| rently executing |

PCSTK | Top of PC stack |

PCSTKP | PC stack pointer |

FADDR* | Fetch address |

DADDR* | Decode address |

LADDR | Loop termination address, code; top of loop |

| address stack |

CURLCNTR | Current loop counter; top of loop count stack |

LCNTR | Loop count for next nested |

| loop |

Data Address Generators | |

DAG1 index registers | |

DAG1 modify registers | |

DAG1 length registers | |

DAG1 base registers | |

DAG2 index registers | |

DAG2 modify registers | |

DAG2 length registers | |

DAG2 base registers | |

Bus Exchange |

|

PX1 | |

PX2 | |

PX | |

Timer |

|

TPERIOD | Timer period |

TCOUNT | Timer counter |

Memory Interface |

|

DMWAIT | Wait state and page size control for data |

| memory |

DMBANK1 | Data memory bank 1 upper boundary |

DMBANK2 | Data memory bank 2 upper boundary |

DMBANK3 | Data memory bank 3 upper boundary |

DMADR* | Copy of last data memory address |

PMWAIT | Wait state and page size control for program |

| memory |

PMBANK1 | Program memory bank 1 upper boundary |

PMADR* | Copy of last program memory address |

System Registers |

|

MODE1 | Mode control bits for |

| isters, interrupt nesting and enable, ALU satu- |

| ration, |

| boundary |

MODE2 | Mode control bits for interrupt sensitivity, |

| cache disable and freeze, timer enable, and I/O |

| flag configuration |

IRPTL | Interrupt latch |

IMASK | Interrupt mask |

IMASKP | Interrupt mask pointer (for nesting) |

ASTAT | Arithmetic status flags, bit test, I/O flag values, |

| and compare accumulator |

STKY | Sticky arithmetic status flags, circular buffer |

| overflow flags, stack status flags (not sticky) |

USTAT1 | User status register l |

USTAT2 | User status register 2 |

|

|

Refer to User’s Manual for

Table IV. ALU Compute Operations

|

|

|

|

Rn = Rx + Ry | Fn = Fx + Fy |

Rn = Rx – Ry | Fn = Fx – Fy |

Rn = Rx + Ry, Rm = Rx – Ry | Fn = Fx + Fy, Fm = Fx – Fy |

Rn = Rx + Ry + CI | Fn = ABS (Fx + Fy) |

Rn = Rx – Ry + CI – l | Fn = ABS (Fx – Fy) |

Rn = (Rx + Ry)/2 | Fn = (Fx + Fy)/2 |

COMP(Rx, Ry) | COMP(Fx, Fy) |

Rn = | Fn = |

Rn = ABS Rx | Fn = ABS Fx |

Rn = PASS Rx | Fn = PASS Fx |

Rn = MIN(Rx, Ry) | Fn = MIN(Fx, Fy) |

Rn = MAX(Rx, Ry) | Fn = MAX(Fx, Fy) |

Rn = CLIP Rx BY Ry | Fn = CLIP Fx BY Fy |

Rn = Rx + CI | Fn = RND Fx |

Rn = Rx + CI – 1 | Fn = SCALB Fx BY Ry |

Rn = Rx + l | Rn = MANT Fx |

Rn = Rx – l | Rn = LOGB Fx |

Rn = Rx AND Ry | Rn = FIX Fx BY Ry |

Rn = Rx OR Ry | Rn = FIX Fx |

Rn = Rx XOR Ry | Fn = FLOAT Rx BY Ry |

Rn = NOT Rx | Fn = FLOAT Rx |

| Fn = RECIPS Fx |

| Fn = RSQRTS Fx |

| Fn = Fx COPYSIGN Fy |

|

|

Rn, Rx, Ry

Fn, Fx, Fy

REV. C |