ADSP-21020

All GND pins should have a low impedance path to ground. A ground plane is required in

The EVDD and IVDD pins should be bypassed to the ground plane using approximately 14

If a VDD plane is not used, the following recommendations apply. Traces from the +5 V supply to the 10 EVDD pins should be designed to satisfy the minimum VDD specification while carrying average dc currents of [IDDEX/10 3 (number of EVDD pins per trace)]. IDDEX is the calculated external supply current. A similar calculation should be made for the four IVDD pins using the IDDIN specification. The traces connecting +5 V to the IVDD pins should be separate from those con- necting to the EVDD pins.

A low frequency bypass capacitor (20 μF tantalum) located near the junction of the IVDD and EVDD traces is also recommended.

Target System Requirements For Use Of

The

KEY (NO PIN 1) | X | CLKIN |

BTMS |

| TMS |

BTCK |

| TCK |

BTRST |

| TRST |

BTDI |

| TDI |

GND |

| TDO |

TOP VIEW

Figure 20. Target Board Connector for EZ-ICE Emulator (Jumpers In Place)

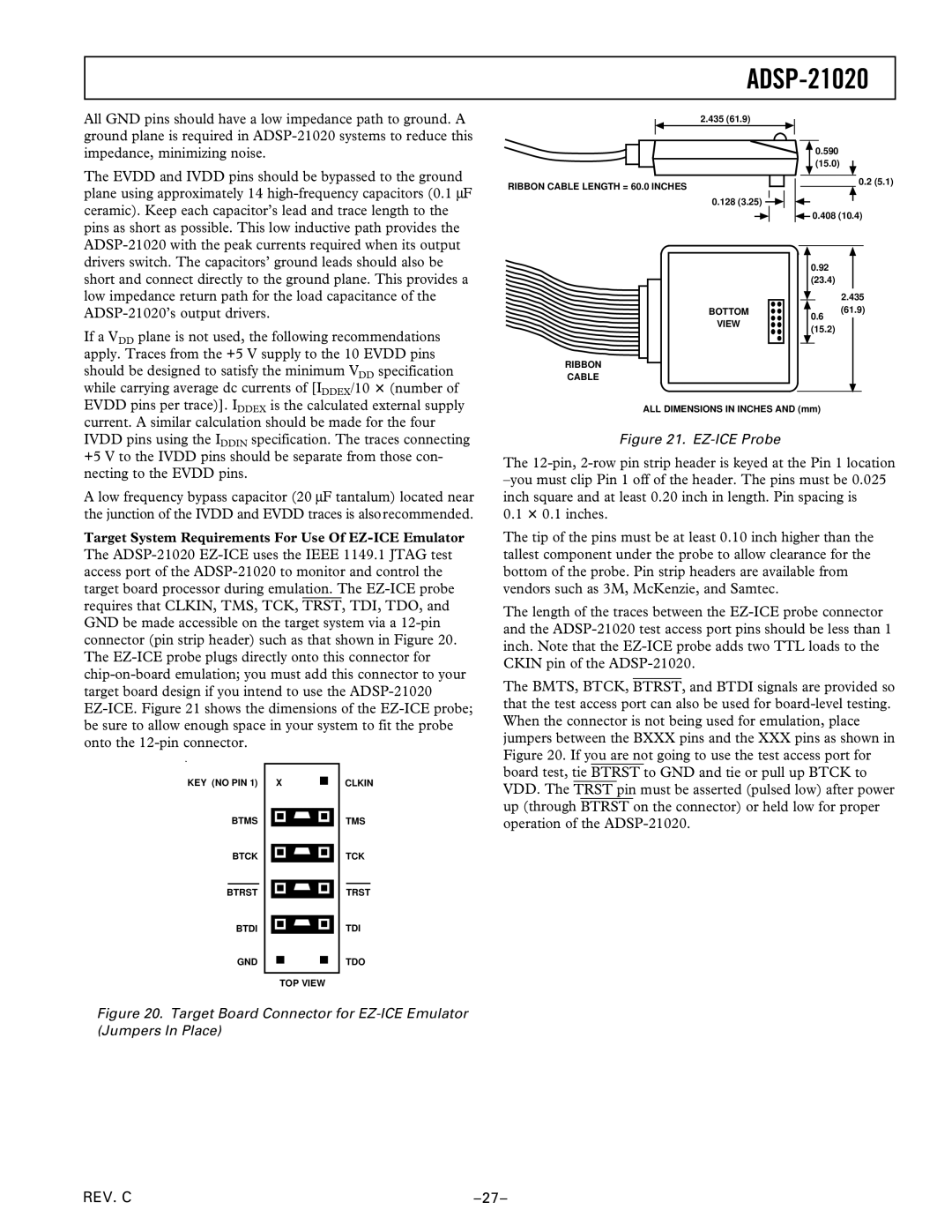

2.435 (61.9)

![]() 0.590 (15.0)

0.590 (15.0)

RIBBON CABLE LENGTH = 60.0 INCHES

0.128 (3.25) ![]()

BOTTOM

VIEW

RIBBON

CABLE

0.2 (5.1)

0.408 (10.4)

0.408 (10.4)

0.92

(23.4)

2.435

(61.9)

0.6

(15.2)

ALL DIMENSIONS IN INCHES AND (mm)

Figure 21. EZ-ICE Probe

The

0.1 3 0.1 inches.

The tip of the pins must be at least 0.10 inch higher than the tallest component under the probe to allow clearance for the bottom of the probe. Pin strip headers are available from vendors such as 3M, McKenzie, and Samtec.

The length of the traces between the

The BMTS, BTCK, BTRST, and BTDI signals are provided so that the test access port can also be used for

REV. C |