Contents

Cypress Semiconductor Corporation

Features

Logic Block Diagram1, 2

Functional Description

Not to scale

Pinouts

Top View

Power Supply Inputs to the Device .0V +20%, -10%

Output Enable, Active LOW. The active LOW

Byte High Enable, Active LOW. Controls DQ15 DQ8

Byte Low Enable, Active LOW. Controls DQ7 DQ0

AutoStore Operation

Device Operation

Sram Read

Sram Write

Software Store

Hardware Recall Power Up

Mode Selection

A15 A09 Mode Power

Noise Considerations

Mode Selection A15 A09

Preventing AutoStore

Data Protection

Range

DC Electrical Characteristics

Maximum Ratings

Operating Range

AC Test Conditions

Data Retention and Endurance

Capacitance

Thermal Resistance

Sram Write Cycle

AC Switching Characteristics

Switching Waveforms

Parameters Sram Read Cycle

Sram Read Cycle #2 CE and OE Controlled 3, 15

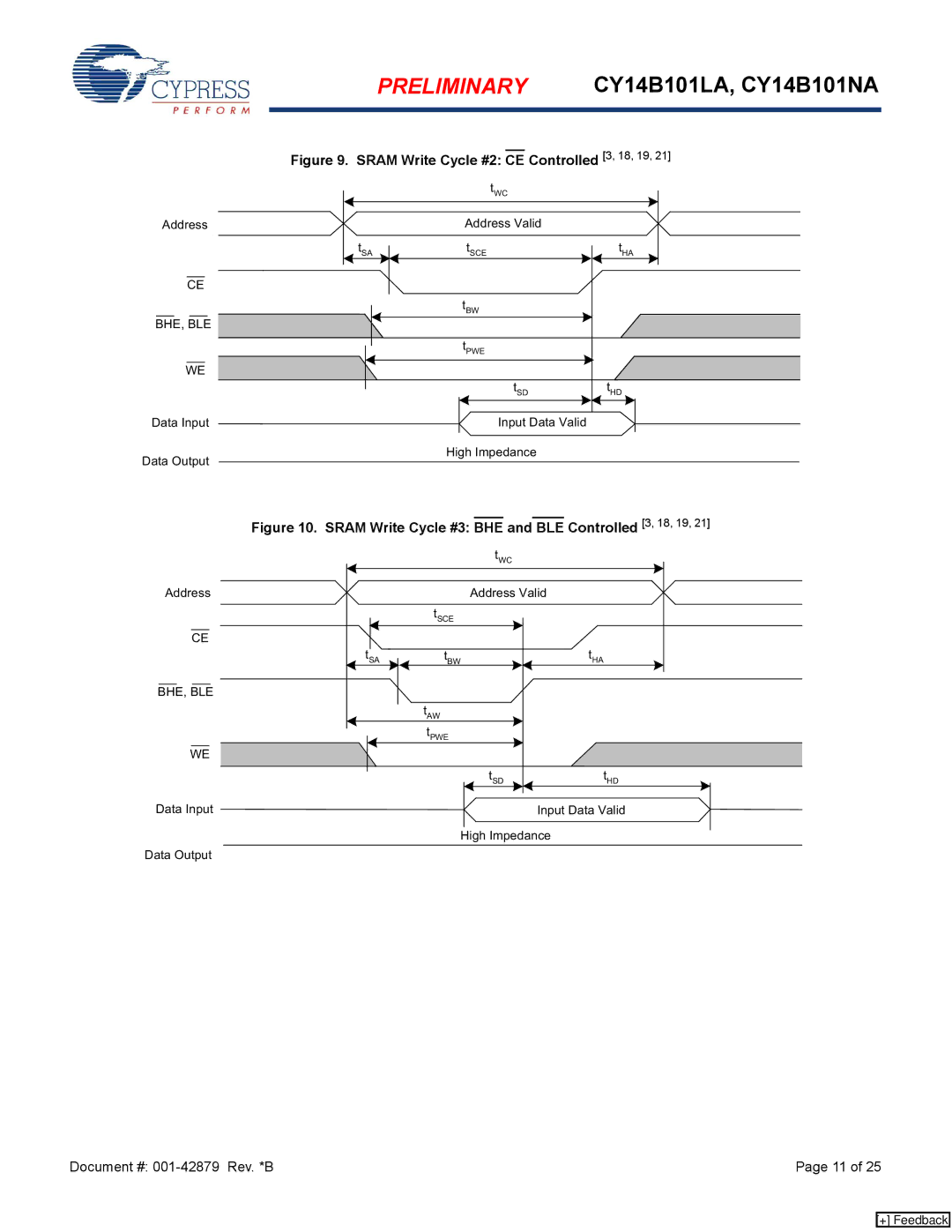

Sram Write Cycle #2 CE Controlled 3, 18, 19

Parameters Description 20 ns 25 ns 45 ns Unit Min Max

AutoStore/Power Up Recall

Description 20 ns 25 ns 45 ns Unit Min Max

Software Controlled STORE/RECALL Cycle

Hardware Store Pulse Width

To Output Active Time when write latch not set

Hardware Store Cycle

Description 20ns 25ns 45ns Unit Min Max

Truth Table For Sram Operations

Truth Table for x8 Configuration Inputs/Outputs Mode Power

Truth Table for x16 Configuration

Inputs/Outputs Mode Power

Ordering Information

CY14B101LA-BA25XC

CY14B101LA-ZS25XCT

CY14B101LA-ZS25XC

CY14B101LA-BA25XCT

CY14B101LA-BA45XC

CY14B101LA-ZS45XCT

CY14B101LA-ZS45XC

CY14B101LA-BA45XCT

Nvsram

Part Numbering Nomenclature

CY 14 B 101L A-ZS 20 X C T

ZS Tsop

Pin Tsop II

Package Diagrams

Ball Fbga 6 mm x 10 mm x 1.2 mm

Pin Ssop

Pin Soic

GVCH/PYRS

Document History

UNC/PYRS

GVCH/AESA

USB

Sales, Solutions, and Legal Information