CY14B104L, CY14B104N

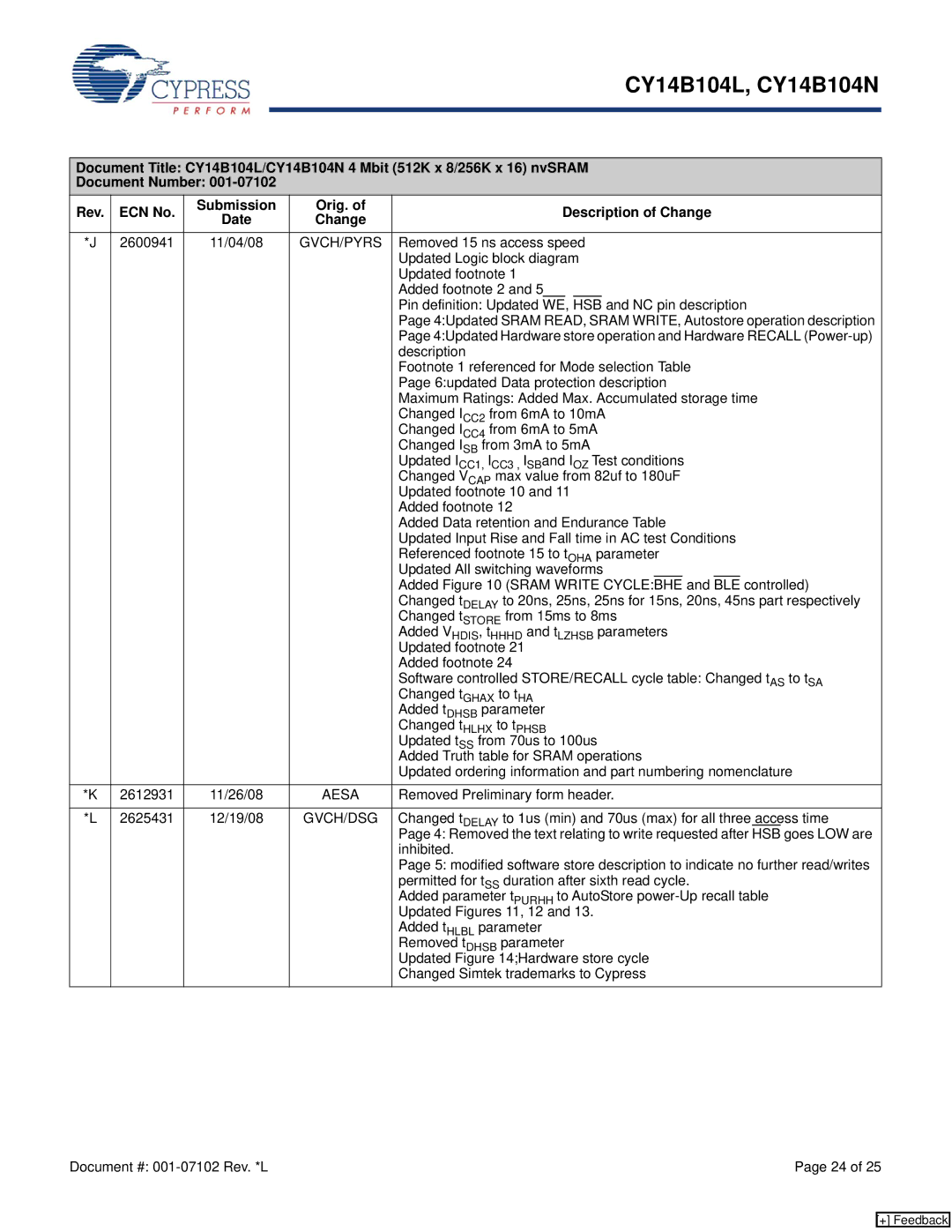

Document Title: CY14B104L/CY14B104N 4 Mbit (512K x 8/256K x 16) nvSRAM

Document Number:

Rev. | ECN No. | Submission | Orig. of |

| Description of Change | |||||||

Date | Change |

| ||||||||||

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

| ||||||||

*J | 2600941 | 11/04/08 | GVCH/PYRS | Removed 15 ns access speed | ||||||||

|

|

|

| Updated Logic block diagram | ||||||||

|

|

|

| Updated footnote 1 | ||||||||

|

|

|

| Added footnote 2 and 5 | ||||||||

|

|

|

| Pin definition: Updated | WE, |

| HSB | and NC pin description | ||||

|

|

|

| Page 4:Updated SRAM READ, SRAM WRITE, Autostore operation description | ||||||||

|

|

|

| Page 4:Updated Hardware store operation and Hardware RECALL | ||||||||

|

|

|

| description | ||||||||

|

|

|

| Footnote 1 referenced for Mode selection Table | ||||||||

|

|

|

| Page 6:updated Data protection description | ||||||||

|

|

|

| Maximum Ratings: Added Max. Accumulated storage time | ||||||||

|

|

|

| Changed ICC2 from 6mA to 10mA | ||||||||

|

|

|

| Changed ICC4 from 6mA to 5mA | ||||||||

|

|

|

| Changed ISB from 3mA to 5mA | ||||||||

|

|

|

| Updated ICC1, ICC3 , ISBand IOZ Test conditions | ||||||||

|

|

|

| Changed VCAP max value from 82uf to 180uF | ||||||||

|

|

|

| Updated footnote 10 and 11 | ||||||||

|

|

|

| Added footnote 12 | ||||||||

|

|

|

| Added Data retention and Endurance Table | ||||||||

|

|

|

| Updated Input Rise and Fall time in AC test Conditions | ||||||||

|

|

|

| Referenced footnote 15 to tOHA parameter | ||||||||

|

|

|

| Updated All switching waveforms |

|

|

|

| ||||

|

|

|

| Added Figure 10 (SRAM WRITE CYCLE:BHE | and BLE controlled) | |||||||

|

|

|

| Changed tDELAY to 20ns, 25ns, 25ns for 15ns, 20ns, 45ns part respectively | ||||||||

|

|

|

| Changed tSTORE from 15ms to 8ms | ||||||||

|

|

|

| Added VHDIS, tHHHD and tLZHSB parameters | ||||||||

|

|

|

| Updated footnote 21 | ||||||||

|

|

|

| Added footnote 24 | ||||||||

|

|

|

| Software controlled STORE/RECALL cycle table: Changed tAS to tSA | ||||||||

|

|

|

| Changed tGHAX to tHA | ||||||||

|

|

|

| Added tDHSB parameter | ||||||||

|

|

|

| Changed tHLHX to tPHSB | ||||||||

|

|

|

| Updated tSS from 70us to 100us | ||||||||

|

|

|

| Added Truth table for SRAM operations | ||||||||

|

|

|

| Updated ordering information and part numbering nomenclature | ||||||||

|

|

|

|

| ||||||||

*K | 2612931 | 11/26/08 | AESA | Removed Preliminary form header. | ||||||||

|

|

|

|

| ||||||||

*L | 2625431 | 12/19/08 | GVCH/DSG | Changed tDELAY to 1us (min) and 70us (max) for all three access time | ||||||||

|

|

|

| Page 4: Removed the text relating to write requested after HSB goes LOW are | ||||||||

|

|

|

| inhibited. | ||||||||

|

|

|

| Page 5: modified software store description to indicate no further read/writes | ||||||||

|

|

|

| permitted for tSS duration after sixth read cycle. | ||||||||

|

|

|

| Added parameter tPURHH to AutoStore | ||||||||

|

|

|

| Updated Figures 11, 12 and 13. | ||||||||

|

|

|

| Added tHLBL parameter | ||||||||

|

|

|

| Removed tDHSB parameter | ||||||||

|

|

|

| Updated Figure 14;Hardware store cycle | ||||||||

|

|

|

| Changed Simtek trademarks to Cypress | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Document #: | Page 24 of 25 |

[+] Feedback