CY14B104L, CY14B104N

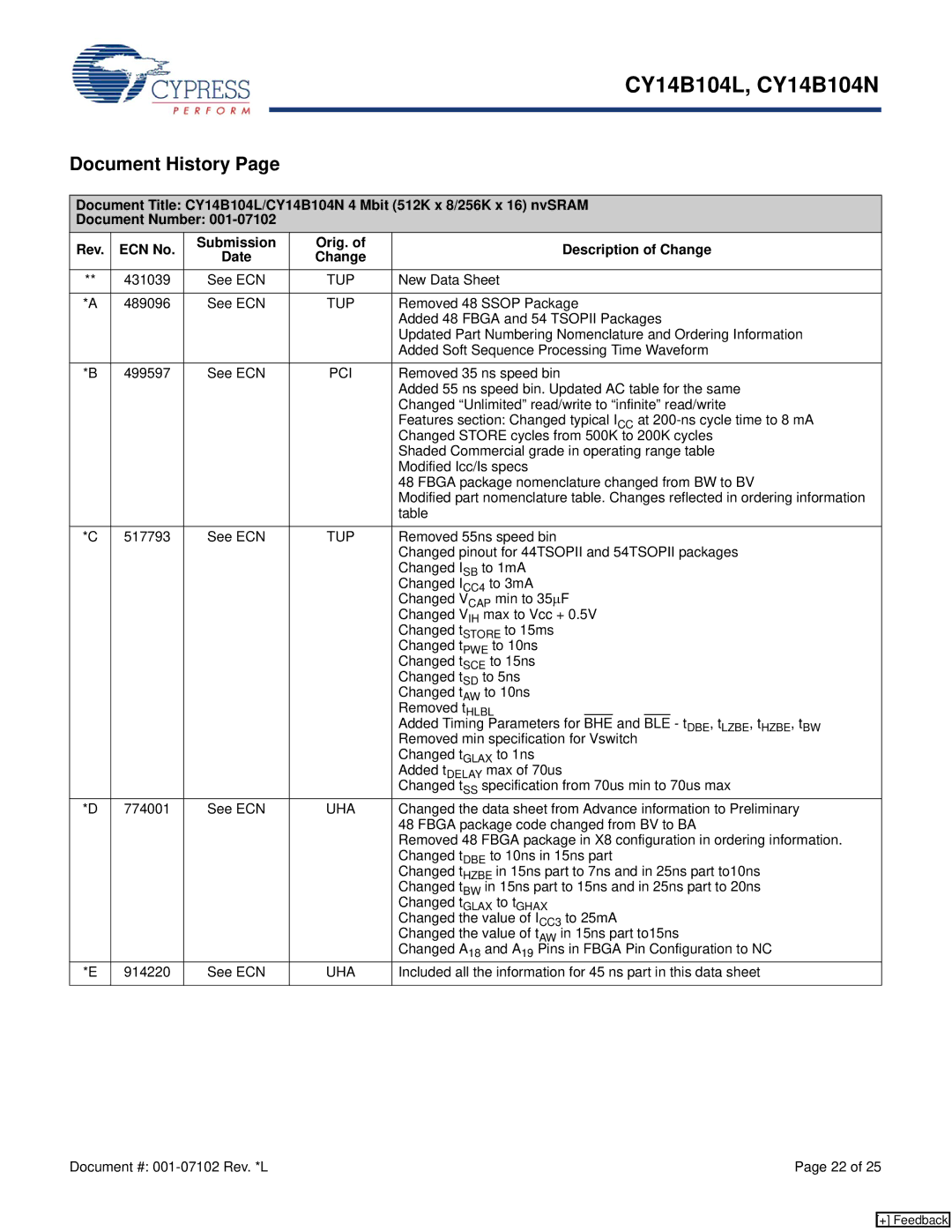

Document History Page

Document Title: CY14B104L/CY14B104N 4 Mbit (512K x 8/256K x 16) nvSRAM

Document Number:

Rev. | ECN No. | Submission | Orig. of | Description of Change | |||||

Date | Change | ||||||||

|

|

|

|

|

|

| |||

|

|

|

|

| |||||

** | 431039 | See ECN | TUP | New Data Sheet | |||||

|

|

|

|

| |||||

*A | 489096 | See ECN | TUP | Removed 48 SSOP Package | |||||

|

|

|

| Added 48 FBGA and 54 TSOPII Packages | |||||

|

|

|

| Updated Part Numbering Nomenclature and Ordering Information | |||||

|

|

|

| Added Soft Sequence Processing Time Waveform | |||||

|

|

|

|

| |||||

*B | 499597 | See ECN | PCI | Removed 35 ns speed bin | |||||

|

|

|

| Added 55 ns speed bin. Updated AC table for the same | |||||

|

|

|

| Changed “Unlimited” read/write to “infinite” read/write | |||||

|

|

|

| Features section: Changed typical ICC at | |||||

|

|

|

| Changed STORE cycles from 500K to 200K cycles | |||||

|

|

|

| Shaded Commercial grade in operating range table | |||||

|

|

|

| Modified Icc/Is specs | |||||

|

|

|

| 48 FBGA package nomenclature changed from BW to BV | |||||

|

|

|

| Modified part nomenclature table. Changes reflected in ordering information | |||||

|

|

|

| table | |||||

|

|

|

|

| |||||

*C | 517793 | See ECN | TUP | Removed 55ns speed bin | |||||

|

|

|

| Changed pinout for 44TSOPII and 54TSOPII packages | |||||

|

|

|

| Changed ISB to 1mA | |||||

|

|

|

| Changed ICC4 to 3mA | |||||

|

|

|

| Changed VCAP min to 35μF | |||||

|

|

|

| Changed VIH max to Vcc + 0.5V | |||||

|

|

|

| Changed tSTORE to 15ms | |||||

|

|

|

| Changed tPWE to 10ns | |||||

|

|

|

| Changed tSCE to 15ns | |||||

|

|

|

| Changed tSD to 5ns | |||||

|

|

|

| Changed tAW to 10ns | |||||

|

|

|

| Removed tHLBL |

|

|

|

| |

|

|

|

| Added Timing Parameters for BHE and BLE - tDBE, tLZBE, tHZBE, tBW | |||||

|

|

|

| Removed min specification for Vswitch | |||||

|

|

|

| Changed tGLAX to 1ns | |||||

|

|

|

| Added tDELAY max of 70us | |||||

|

|

|

| Changed tSS specification from 70us min to 70us max | |||||

*D | 774001 | See ECN | UHA | Changed the data sheet from Advance information to Preliminary | |||||

|

|

|

| 48 FBGA package code changed from BV to BA | |||||

|

|

|

| Removed 48 FBGA package in X8 configuration in ordering information. | |||||

|

|

|

| Changed tDBE to 10ns in 15ns part | |||||

|

|

|

| Changed tHZBE in 15ns part to 7ns and in 25ns part to10ns | |||||

|

|

|

| Changed tBW in 15ns part to 15ns and in 25ns part to 20ns | |||||

|

|

|

| Changed tGLAX to tGHAX | |||||

|

|

|

| Changed the value of ICC3 to 25mA | |||||

|

|

|

| Changed the value of tAW in 15ns part to15ns | |||||

|

|

|

| Changed A18 and A19 Pins in FBGA Pin Configuration to NC | |||||

*E | 914220 | See ECN | UHA | Included all the information for 45 ns part in this data sheet | |||||

|

|

|

|

|

|

|

|

| |

Document #: | Page 22 of 25 |

[+] Feedback