CY7C1161V18, CY7C1176V18

CY7C1163V18, CY7C1165V18

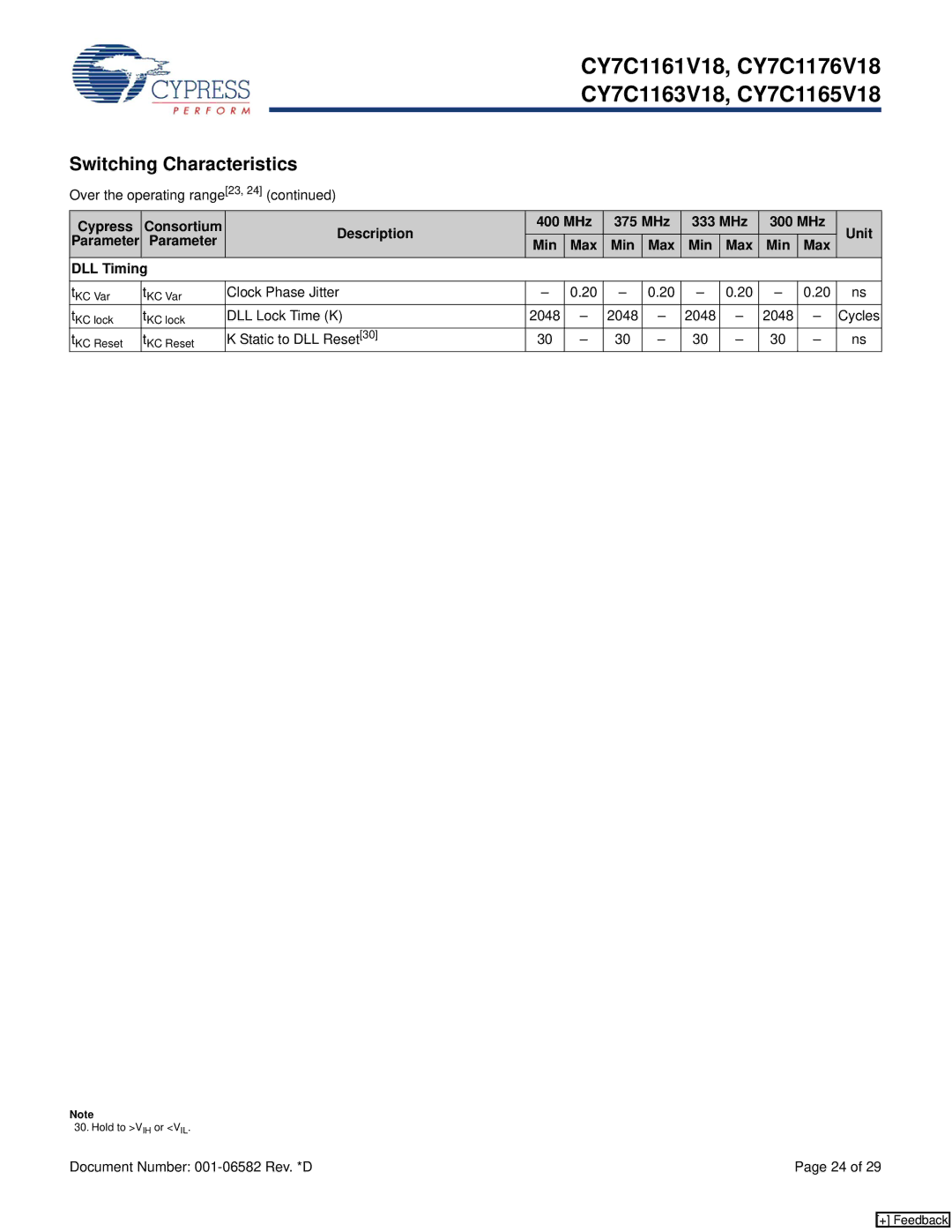

Switching Characteristics

Over the operating range[23, 24] (continued)

Cypress | Consortium | Description | 400 MHz | 375 MHz | 333 MHz | 300 MHz | Unit | ||||

Parameter | Parameter | Min | Max | Min | Max | Min | Max | Min | Max | ||

DLL Timing |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

tKC Var | tKC Var | Clock Phase Jitter | – | 0.20 | – | 0.20 | – | 0.20 | – | 0.20 | ns |

tKC lock | tKC lock | DLL Lock Time (K) | 2048 | – | 2048 | – | 2048 | – | 2048 | – | Cycles |

tKC Reset | tKC Reset | K Static to DLL Reset[30] | 30 | – | 30 | – | 30 | – | 30 | – | ns |

Note

30. Hold to >VIH or <VIL.

Document Number: | Page 24 of 29 |

[+] Feedback