CY7C1364C

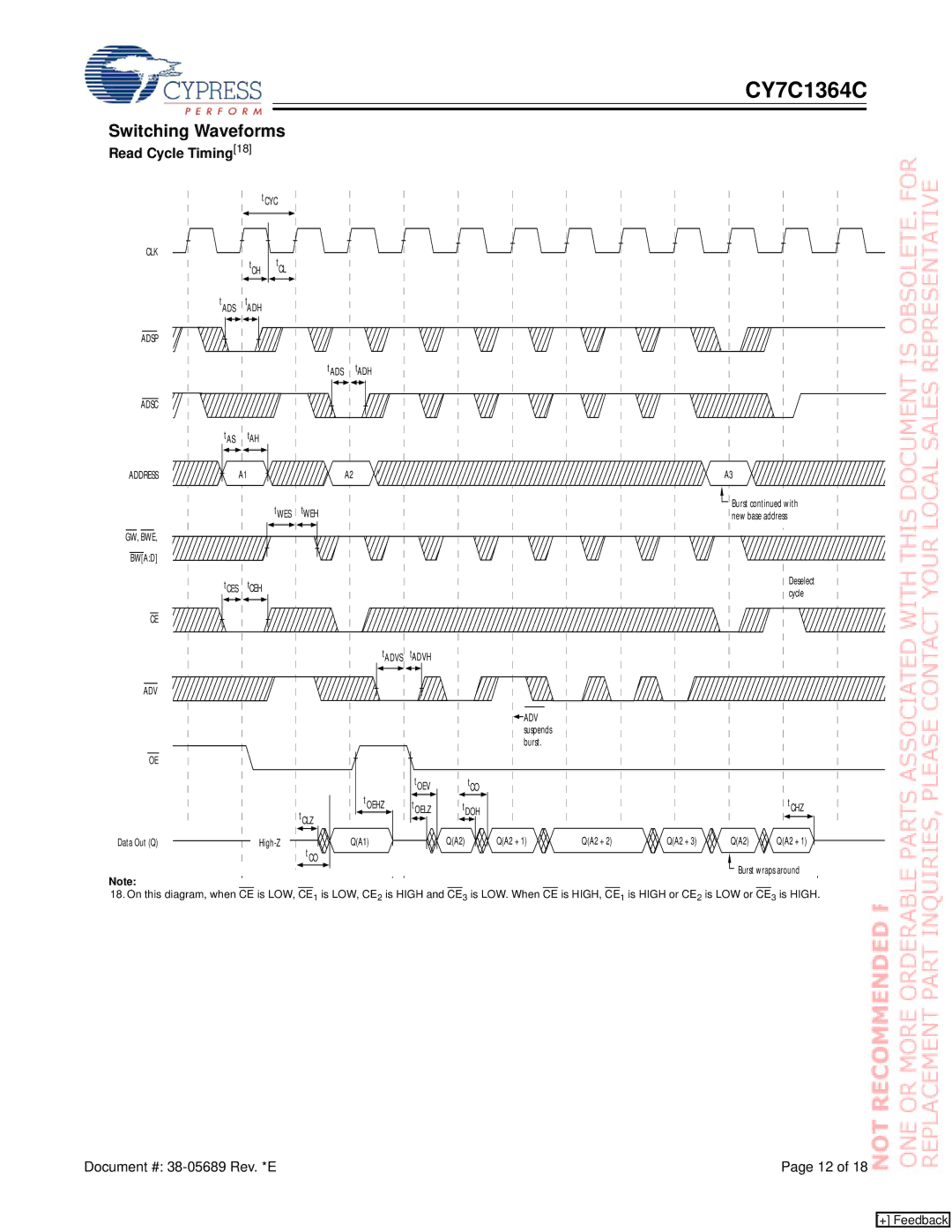

Switching Waveforms

Read Cycle Timing[18]

CLK

ADSP

ADSC

tCYC

tCH |

| tCL | |

|

|

|

|

tADS tADH

tADS tADH

ADDRESS

GW, BWE,

BW[A:D]

CE

ADV

OE

Data Out (Q)

Note:

tAS tAH

A1 | A2 |

tWES tWEH

tCES tCEH

tADVS tADVH

|

| tOEV | tCO |

| tOEHZ | tOELZ | tDOH |

| tCLZ |

|

|

Q(A1) |

| Q(A2) | |

| tCO |

|

|

A3

Burst continued with new base address

Deselect cycle

![]() ADV suspends burst.

ADV suspends burst.

tCHZ

Q(A2 + 1) | Q(A2 + 2) | Q(A2 + 3) | Q(A2) | Q(A2 + 1) |

Burst wraps around

18. On this diagram, when CE is LOW, CE1 is LOW, CE2 is HIGH and CE3 is LOW. When CE is HIGH, CE1 is HIGH or CE2 is LOW or CE3 is HIGH.

Document #: | Page 12 of 18 |

[+] Feedback