CY7C1382DV25, CY7C1380DV25, CY7C1382FV25, CY7C1380FV25 specifications

The Cypress CY7C1380FV25, CY7C1382FV25, CY7C1380DV25, and CY7C1382DV25 are high-performance static random access memory (SRAM) devices distinguished by their reliability and efficiency. These components are designed for applications requiring fast data storage and retrieval, making them ideal for embedded systems, communication devices, and various consumer electronics.One of the main features of these SRAMs is their access time. The CY7C1380FV25 and CY7C1382FV25 models come with a super-fast access time of 25 nanoseconds, ensuring that data can be retrieved with minimal delay. This characteristic is crucial for high-speed applications, such as networking equipment and automotive systems, where rapid data processing is essential.

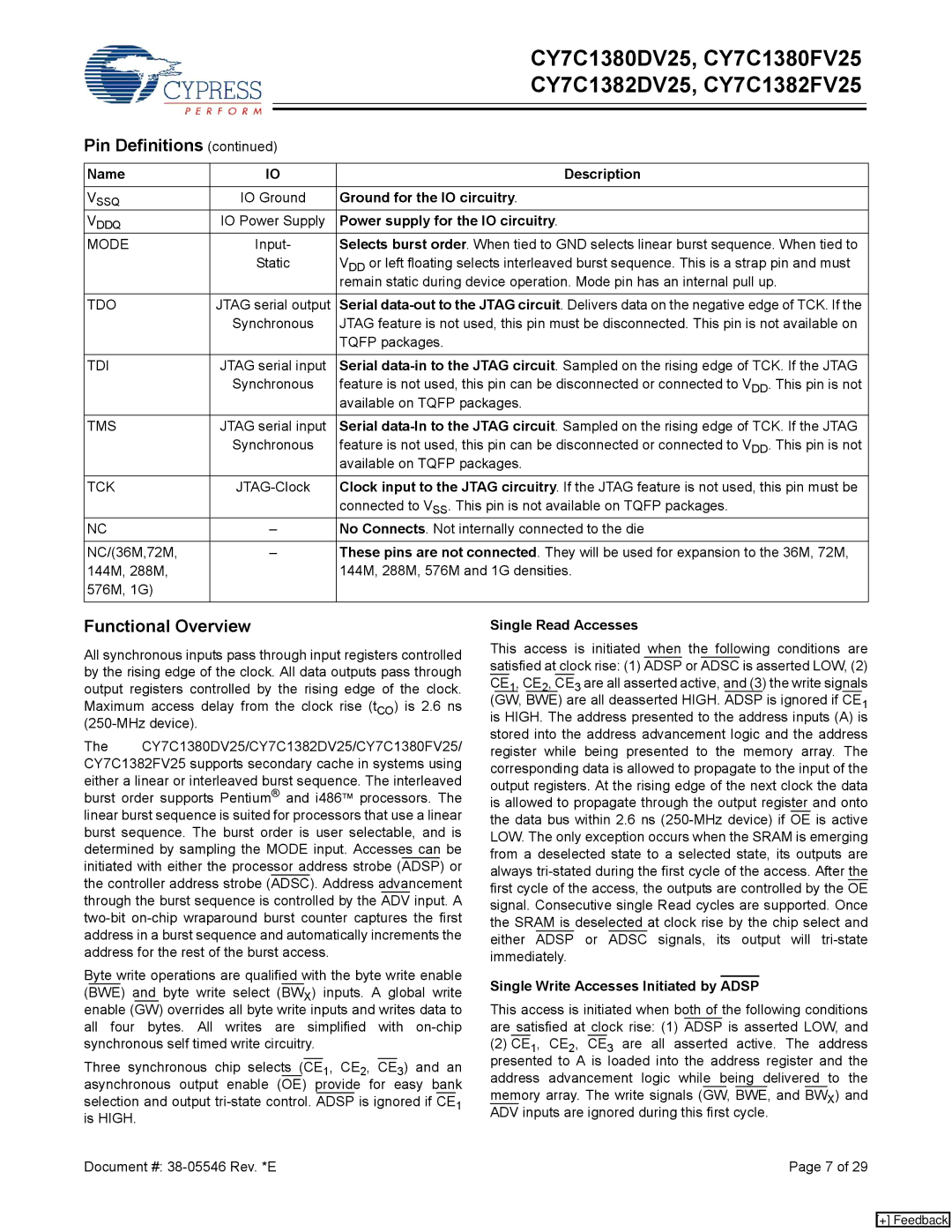

Both families of devices offer a competitive data width configuration, with CY7C1380 series providing 8 bits and CY7C1382 series providing 16 bits. This flexibility allows designers to choose the appropriate configuration based on their specific application requirements. Additionally, they support a wide voltage range for ease of integration into various systems.

The CY7C1380FV25 and CY7C1380DV25 devices feature low power consumption, which is vital for battery-operated devices. With their advanced CMOS technology, they exhibit reduced static power requirements, helping to prolong battery life and improve overall system efficiency. The IDD (supply current) ratings are particularly low, making them suitable for energy-sensitive applications.

A notable characteristic of the Cypress memory devices is their asynchronous read and write operations, providing simple interfacing in a variety of designs. They are designed to operate under a wide range of temperature conditions; thus, they are well-suited for industrial applications where temperature fluctuations might be a concern.

Furthermore, the CY7C1382FV25 and CY7C1382DV25 models include features like burst mode capability, enabling faster sequential access, which is beneficial for high-speed data processing tasks. This allows these SRAMs to deliver enhanced performance critical in applications like video processing and real-time data acquisition.

In summary, the Cypress CY7C1380FV25, CY7C1382FV25, CY7C1380DV25, and CY7C1382DV25 are distinguished by their fast access times, low power consumption, and flexible data widths. Their advanced technologies and characteristics make them a reliable choice for a diverse range of high-performance applications, ensuring that engineers can effectively address their design challenges while meeting the demands of modern electronics.