CY7C1470BV25

CY7C1472BV25, CY7C1474BV25

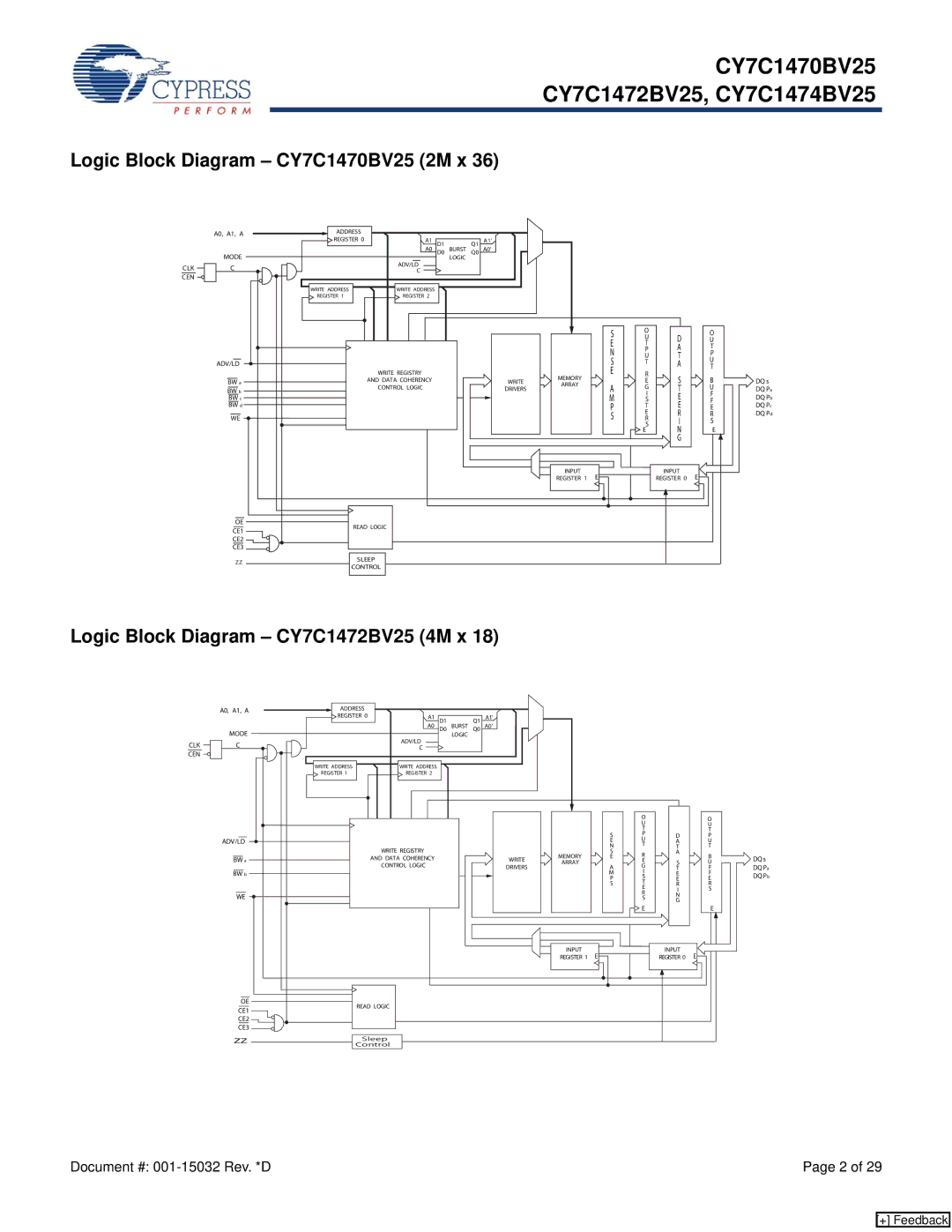

Logic Block Diagram – CY7C1470BV25 (2M x 36)

| A0, A1, A | ADDRESS |

|

|

|

|

|

|

|

|

|

|

|

| REGISTER 0 | A1 | D1 |

| Q1 | A1' |

|

|

|

|

|

| MODE |

| A0 | D0 | BURST | Q0 | A0' |

|

|

|

|

|

|

| ADV/LD |

| LOGIC |

|

|

|

|

|

|

| |

CLK | C |

|

|

|

|

|

|

|

|

|

| |

| C |

|

|

|

|

|

|

|

|

| ||

CEN |

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

| |

|

| WRITE ADDRESS | WRITE ADDRESS |

|

|

|

|

|

|

|

|

|

|

| REGISTER 1 | REGISTER 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| S | O |

| O |

|

|

|

|

|

|

|

|

| U | D | ||

|

|

|

|

|

|

|

|

| E | T | U | |

|

|

|

|

|

|

|

|

| P | A | T | |

|

|

|

|

|

|

|

|

| N | |||

|

|

|

|

|

|

|

|

| U | T | P | |

| ADV/LD |

|

|

|

|

|

|

| S | T | A | U |

|

|

|

|

|

|

|

| R | T | |||

|

|

| WRITE REGISTRY |

|

|

|

| MEMORY | E | S | B | |

| BW a |

| AND DATA COHERENCY |

|

|

| WRITE |

| E | |||

|

|

|

|

| ARRAY |

| ||||||

| BW b |

| CONTROL LOGIC |

|

|

| DRIVERS | A | G | T | U | |

|

|

|

|

|

|

| I | F | ||||

| BW c |

|

|

|

|

|

|

| M | S | E | |

|

|

|

|

|

|

|

| F | ||||

| BW d |

|

|

|

|

|

|

| P | E | E | E |

|

|

|

|

|

|

|

|

| T | R | R | |

| WE |

|

|

|

|

|

|

| S | R | ||

|

|

|

|

|

|

|

|

|

| S | I | S |

|

|

|

|

|

|

|

|

|

| E | N | E |

|

|

|

|

|

|

|

|

|

|

| G |

|

|

|

|

|

|

|

|

| INPUT | E |

| INPUT | E |

|

|

|

|

|

|

|

| REGISTER 1 |

| REGISTER 0 | ||

| OE | READ LOGIC |

|

|

|

|

|

|

|

|

| |

| CE1 |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| |

| CE2 |

|

|

|

|

|

|

|

|

|

|

|

| CE3 |

|

|

|

|

|

|

|

|

|

|

|

| ZZ | SLEEP |

|

|

|

|

|

|

|

|

| |

| CONTROL |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| ||

DQ s DQ Pa DQ Pb DQ Pc DQ Pd

Logic Block Diagram – CY7C1472BV25 (4M x 18)

| A0, A1, A | ADDRESS |

|

|

|

|

|

|

|

|

|

| |

|

| REGISTER 0 | A1 | D1 |

| Q1 | A1' |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| ||||

| MODE |

|

| A0 | D0 | BURST | Q0 | A0' |

|

|

|

|

|

|

|

| ADV/LD |

| LOGIC |

|

|

|

|

|

|

| |

CLK | C |

|

|

|

|

|

|

|

|

|

|

| |

|

| C |

|

|

|

|

|

|

|

|

| ||

CEN |

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| WRITE ADDRESS |

| WRITE ADDRESS |

|

|

|

|

|

|

|

|

|

|

| REGISTER 1 |

| REGISTER 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| O |

| O |

|

|

|

|

|

|

|

|

|

|

| U |

| U |

|

|

|

|

|

|

|

|

|

| S | T | D | T |

|

|

|

|

|

|

|

|

|

| P | P | ||

| ADV/LD |

|

|

|

|

|

|

|

| E | U | A | U |

|

|

|

| WRITE REGISTRY |

|

|

|

|

| N | T | T | T |

|

|

|

|

|

|

|

| MEMORY | S | R | A | B | |

| BW a |

|

| AND DATA COHERENCY |

|

|

| WRITE | E |

| |||

|

|

|

|

|

| ARRAY |

| E | S | U | |||

|

|

|

| CONTROL LOGIC |

|

|

| DRIVERS | A | G | |||

|

|

|

|

|

|

|

| T | F | ||||

| BW b |

|

|

|

|

|

|

|

| M | I | E | F |

|

|

|

|

|

|

|

|

|

| P | S | E | E |

|

|

|

|

|

|

|

|

|

| S | T | R | R |

|

|

|

|

|

|

|

|

|

|

| E | I | S |

| WE |

|

|

|

|

|

|

|

|

| R | N |

|

|

|

|

|

|

|

|

|

|

| S |

| ||

|

|

|

|

|

|

|

|

|

|

|

| G |

|

|

|

|

|

|

|

|

|

|

|

| E |

| E |

|

|

|

|

|

|

|

|

| INPUT | E |

| INPUT | E |

|

|

|

|

|

|

|

|

| REGISTER 1 |

| REGISTER 0 | ||

| OE |

| READ LOGIC |

|

|

|

|

|

|

|

|

| |

| CE1 |

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| |

| CE2 |

|

|

|

|

|

|

|

|

|

|

|

|

| CE3 |

|

|

|

|

|

|

|

|

|

|

|

|

| ZZ |

| Sleep |

|

|

|

|

|

|

|

|

| |

|

|

| Control |

|

|

|

|

|

|

|

|

| |

DQ s DQ Pa DQ Pb

Document #: | Page 2 of 29 |

[+] Feedback