CY7C1470BV25

CY7C1472BV25, CY7C1474BV25

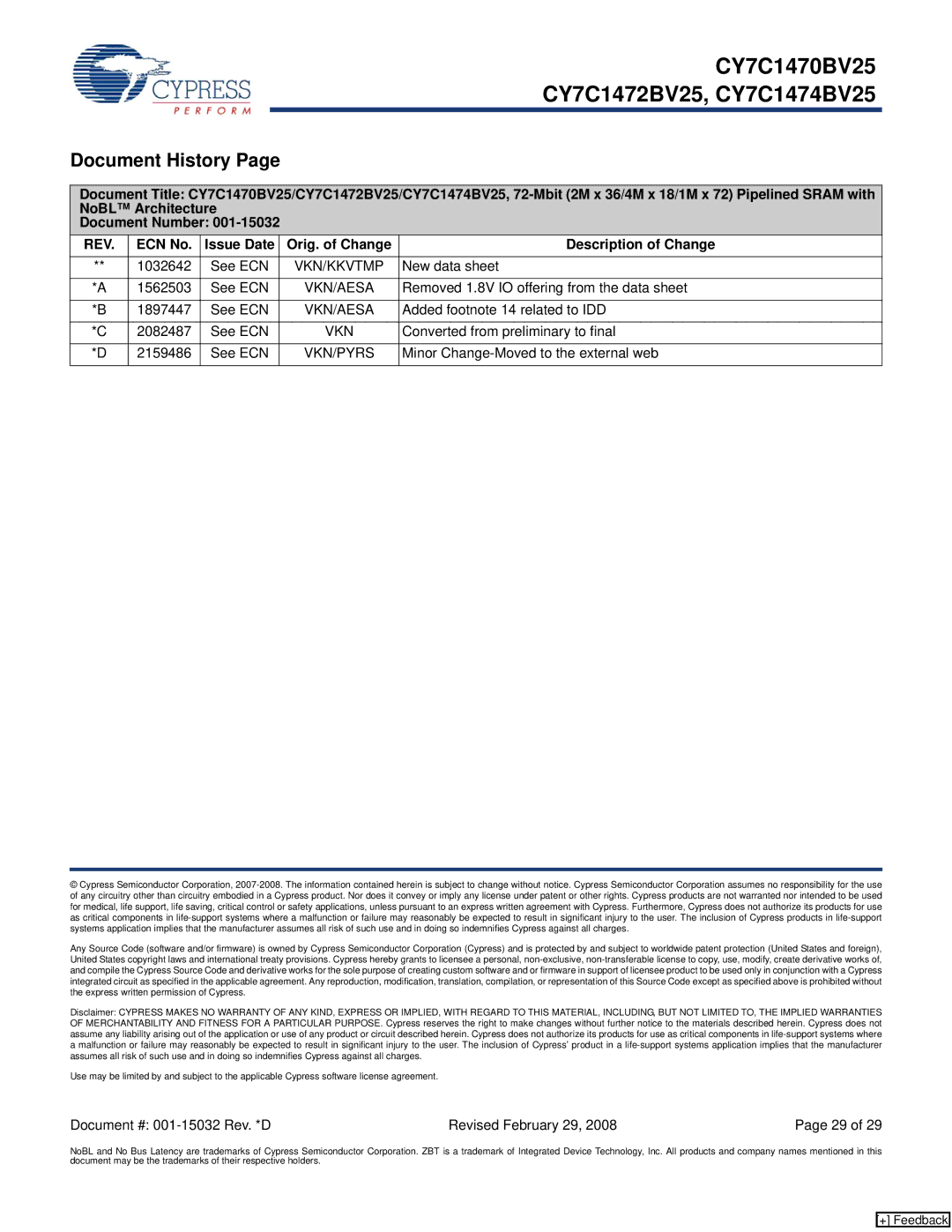

Document History Page

Document Title: CY7C1470BV25/CY7C1472BV25/CY7C1474BV25, 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL™ Architecture

Document Number: 001-15032

REV. | ECN No. | Issue Date | Orig. of Change | Description of Change |

** | 1032642 | See ECN | VKN/KKVTMP | New data sheet |

| | | | |

*A | 1562503 | See ECN | VKN/AESA | Removed 1.8V IO offering from the data sheet |

| | | | |

*B | 1897447 | See ECN | VKN/AESA | Added footnote 14 related to IDD |

| | | | |

*C | 2082487 | See ECN | VKN | Converted from preliminary to final |

| | | | |

*D | 2159486 | See ECN | VKN/PYRS | Minor Change-Moved to the external web |

| | | | |

© Cypress Semiconductor Corporation, 2007-2008. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress’ product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 001-15032 Rev. *D | Revised February 29, 2008 | Page 29 of 29 |

NoBL and No Bus Latency are trademarks of Cypress Semiconductor Corporation. ZBT is a trademark of Integrated Device Technology, Inc. All products and company names mentioned in this document may be the trademarks of their respective holders.