FUNCTIONAL DESCRIPTION

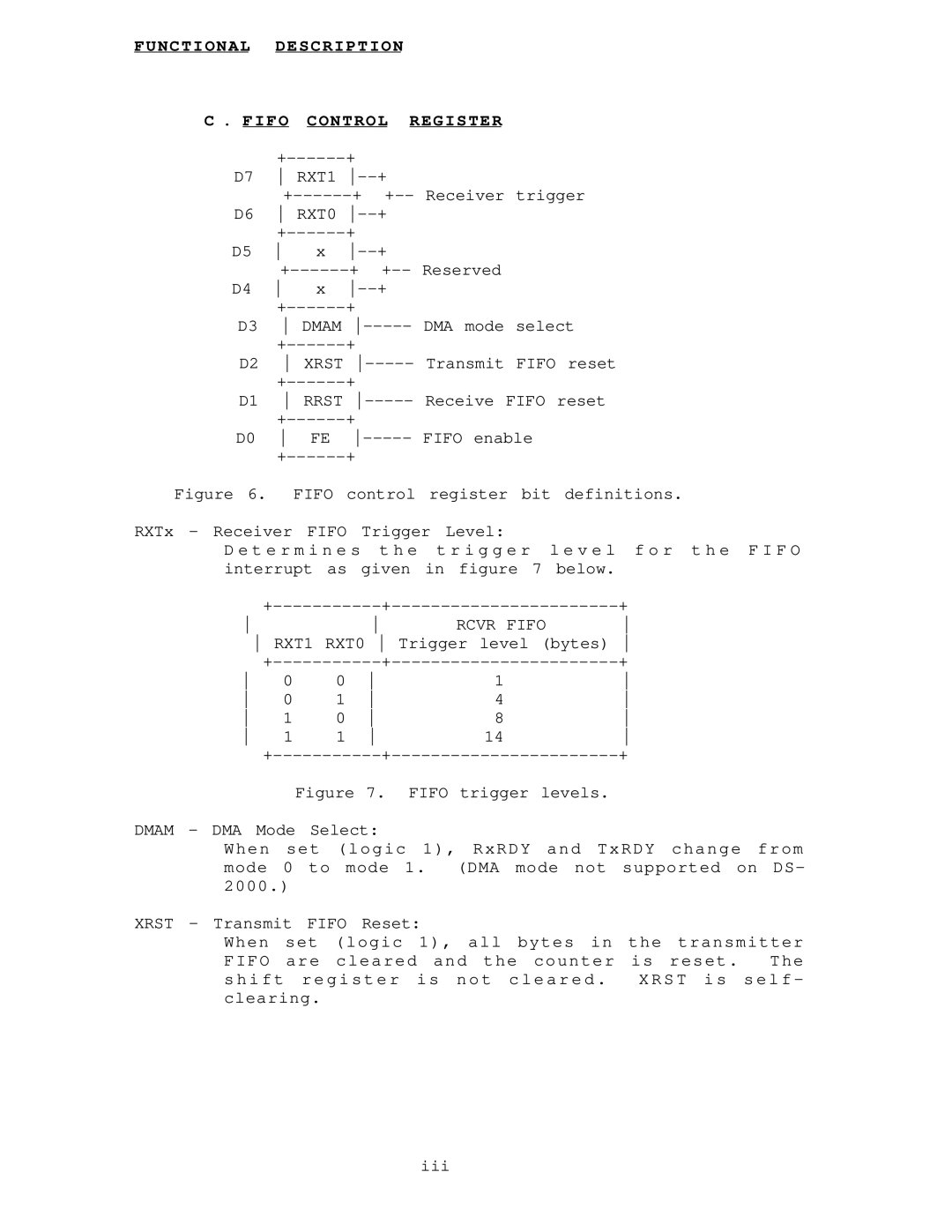

C . FIFO | CONTROL | REGISTER |

|

| |||

| + |

|

|

|

| ||

D7 | RXT1 | + |

|

|

| ||

| + | Receiver | trigger | ||||

D6 | RXT0 | + |

|

|

| ||

| + |

|

|

|

| ||

D5 | x | + |

|

|

| ||

| + | Reserved |

|

| |||

D4 | x | + |

|

|

| ||

| + |

|

|

|

| ||

D3 | DMAM | DMA mode | select | ||||

| + |

|

|

|

| ||

D2 | XRST | Transmit | FIFO | reset | |||

| + |

|

|

|

| ||

D1 | RRST | Receive | FIFO | reset | |||

| + |

|

|

|

| ||

D0 | FE | FIFO enable |

| ||||

| + |

|

|

|

| ||

Figure 6. FIFO control register bit definitions.

RXTx - Receiver | FIFO | Trigger Level: |

|

| ||

D e t e r m i n e s t h e t r i g g e r l e v e l f o r t h e F I F O | ||||||

interrupt as | given in | figure | 7 below. |

| ||

|

| + | ||||

|

| RCVR FIFO | ||||

| RXT1 RXT0 Trigger level | (bytes) | ||||

|

| + | ||||

0 | 0 | 1 |

| |||

0 | 1 | 4 |

| |||

1 | 0 | 8 |

| |||

1 | 1 | 14 |

| |||

|

| + | ||||

|

| Figure | 7. FIFO | trigger | levels. |

|

DMAM - DMA Mode Select:

When set (logic 1), RxRDY and TxRDY change from mode 0 to mode 1. (DMA mode not supported on DS- 2000.)

XRST - Transmit FIFO Reset:

When set (logic 1), all bytes in the transmitter

FIFO are cleared and the counter | is reset. The |

s h i f t r e g i s t e r i s n o t c l e a r e d . | X R S T i s s e l f - |

clearing. |

|

iii