|

|

|

| FUNCTIONAL | DESCRIPTION | |||

|

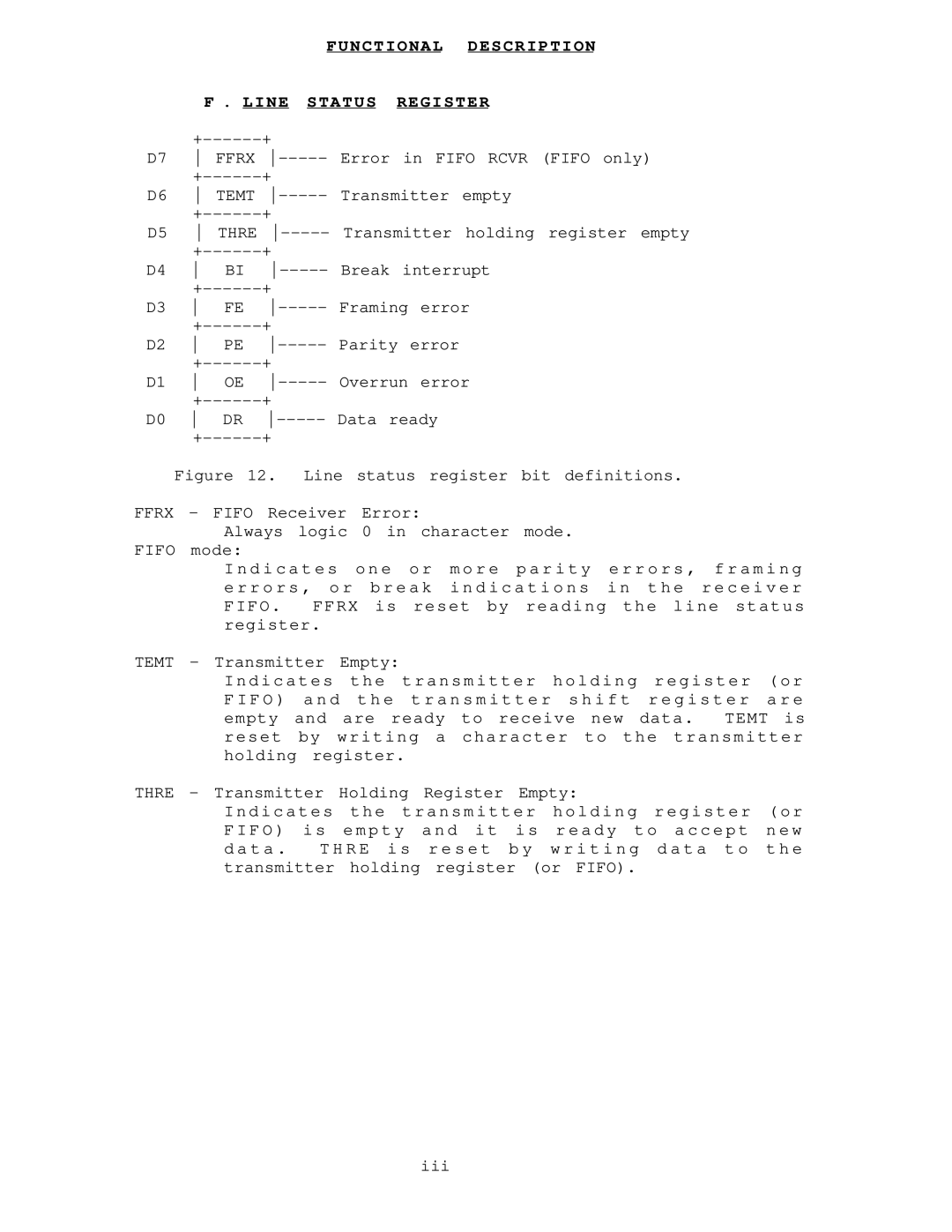

| F . LINE | STATUS | REGISTER |

| |||

| + |

|

|

|

|

| ||

D7 | FFRX | Error | in FIFO RCVR | (FIFO only) | ||||

| + |

|

|

|

|

| ||

D6 | TEMT | Transmitter | empty |

| ||||

| + |

|

|

|

|

| ||

D5 | THRE | Transmitter | holding | register empty | ||||

| + |

|

|

|

|

| ||

D4 | BI | Break | interrupt |

| ||||

| + |

|

|

|

|

| ||

D3 | FE | Framing | error |

| ||||

| + |

|

|

|

|

| ||

D2 | PE | Parity | error |

|

| |||

| + |

|

|

|

|

| ||

D1 | OE | Overrun | error |

| ||||

| + |

|

|

|

|

| ||

D0 | DR | Data ready |

|

| ||||

| + |

|

|

|

|

| ||

Figure 12. Line status register bit definitions.

FFRX - | FIFO Receiver Error: | |||

|

| Always logic 0 in character mode. | ||

FIFO | mode: |

|

| |

|

| I n d i c a t e s o n e o r m o r e p a r i t y e r r o r s , f r a m i n g | ||

|

| e r r o r s , o r b r e a k i n d i c a t i o n s i n t h e r e c e i v e r | ||

|

| FIFO. FFRX is reset by reading the line status | ||

|

| register. |

| |

TEMT | - | Transmitter | Empty: | |

|

| Indicates | the transmitter holding register (or | |

|

| F I F O ) a n d t h e t r a n s m i t t e r s h i f t r e g i s t e r a r e | ||

|

| empty and are ready to receive new data. TEMT is | ||

|

| reset by writing a character to the transmitter | ||

|

| holding | register. | |

THRE - | Transmitter Holding Register Empty: | |||

|

| Indicates | the transmitter holding register (or | |

|

| F I F O ) i s e m p t y a n d i t i s r e a d y t o a c c e p t n e w | ||

|

| d a t a . | T H R E i s r e s e t b y w r i t i n g d a t a t o t h e | |

|

| transmitter | holding register (or FIFO). | |

iii