|

| FUNCTIONAL DESCRIPTION |

|

| |

RRST | - | Receive FIFO Reset: |

|

|

|

|

| W h e n s e t ( l o g i c 1 ) , a l l b y t e s i n t h e r e c e i v e r | |||

|

| FIFO are cleared | and the counter | is reset. | The |

|

| s h i f t r e g i s t e r i s n o t c l e a r e d . | R R S T i s s e l f - | ||

|

| clearing. |

|

|

|

FE | - | FIFO Enable: |

|

|

|

|

| W h e n s e t ( l o g i c 1 ) , e n a b l e s t r a n s m i t t e r a n d | |||

|

| r e c e i v e r F I F O s . | W h e n c l e a r e d ( l o g i c 0 ) , a l l | ||

|

| bytes in both FIFOs are cleared. | This bit | must | |

|

| b e s e t w h e n o t h e r b i t s i n t h e F I F O c o n t r o l | |||

|

| r e g i s t e r a r e w r i t t e n t o o r t h e b i t s w i l l b e | |||

|

| ignored. |

|

|

|

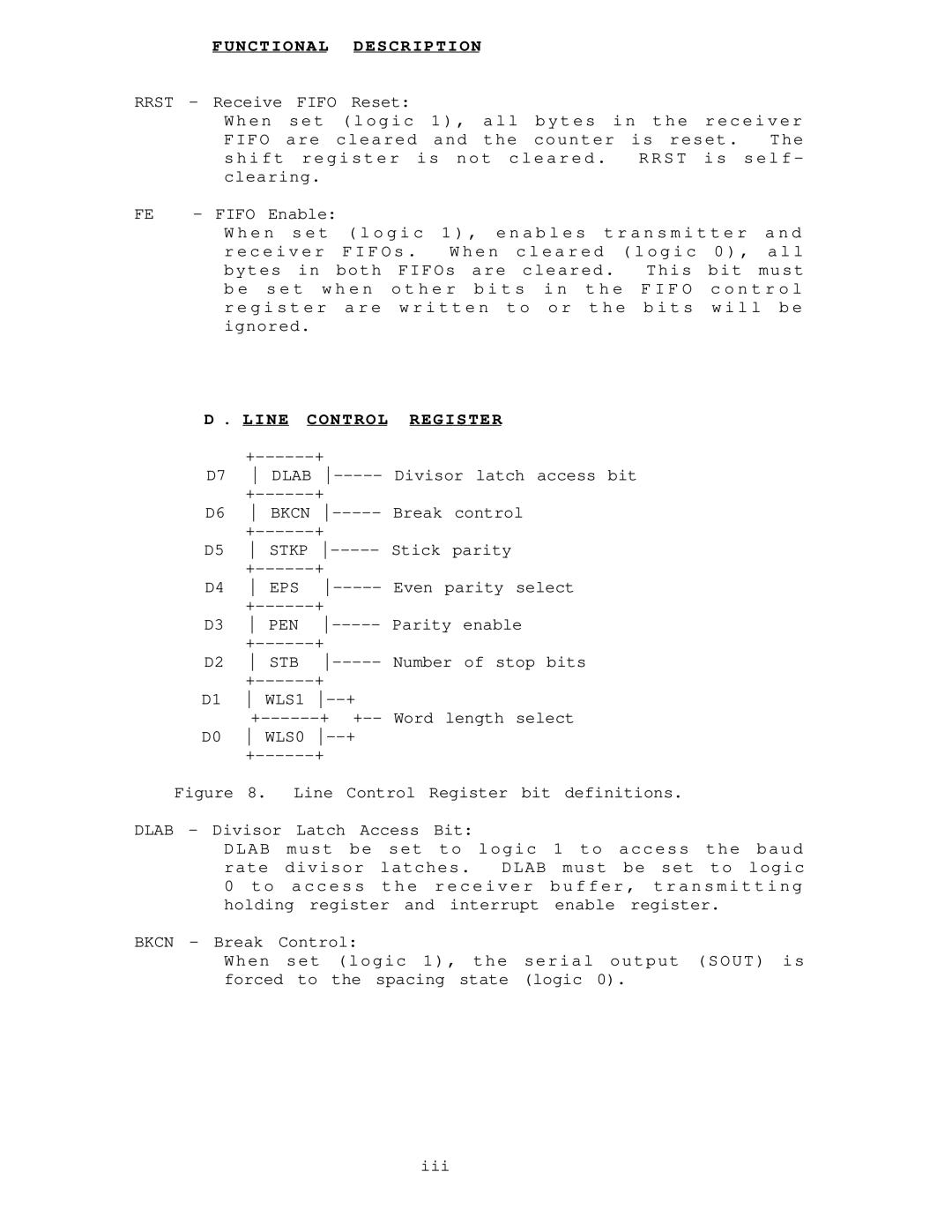

D . LINE CONTROL | REGISTER |

| ||||||

| + |

|

|

|

|

| ||

D7 | DLAB | Divisor latch | access bit | |||||

| + |

|

|

|

|

| ||

D6 | BKCN | Break |

| control |

| |||

| + |

|

|

|

|

| ||

D5 | STKP | Stick |

| parity |

| |||

| + |

|

|

|

|

| ||

D4 | EPS | Even | parity select | |||||

| + |

|

|

|

|

| ||

D3 | PEN | Parity | enable |

| ||||

| + |

|

|

|

|

| ||

D2 | STB | Number | of stop | bits | ||||

| + |

|

|

|

|

| ||

D1 | WLS1 | + |

|

|

|

| ||

| + | Word | length select | |||||

D0 | WLS0 | + |

|

|

|

| ||

| + |

|

|

|

|

| ||

Figure 8. Line Control Register bit definitions.

DLAB - Divisor Latch Access Bit:

DLAB | must be | set to logic 1 to access the baud |

rate | divisor | latches. DLAB must be set to logic |

0 t o a c c e s s t h e r e c e i v e r b u f f e r , t r a n s m i t t i n g | ||

holding register and interrupt enable register. | ||

BKCN - Break | Control: |

|

When set (logic 1), the serial output (SOUT) is | ||

forced to the | spacing state (logic 0). | |

iii