FUNCTIONAL | DESCRIPTION |

| ||||

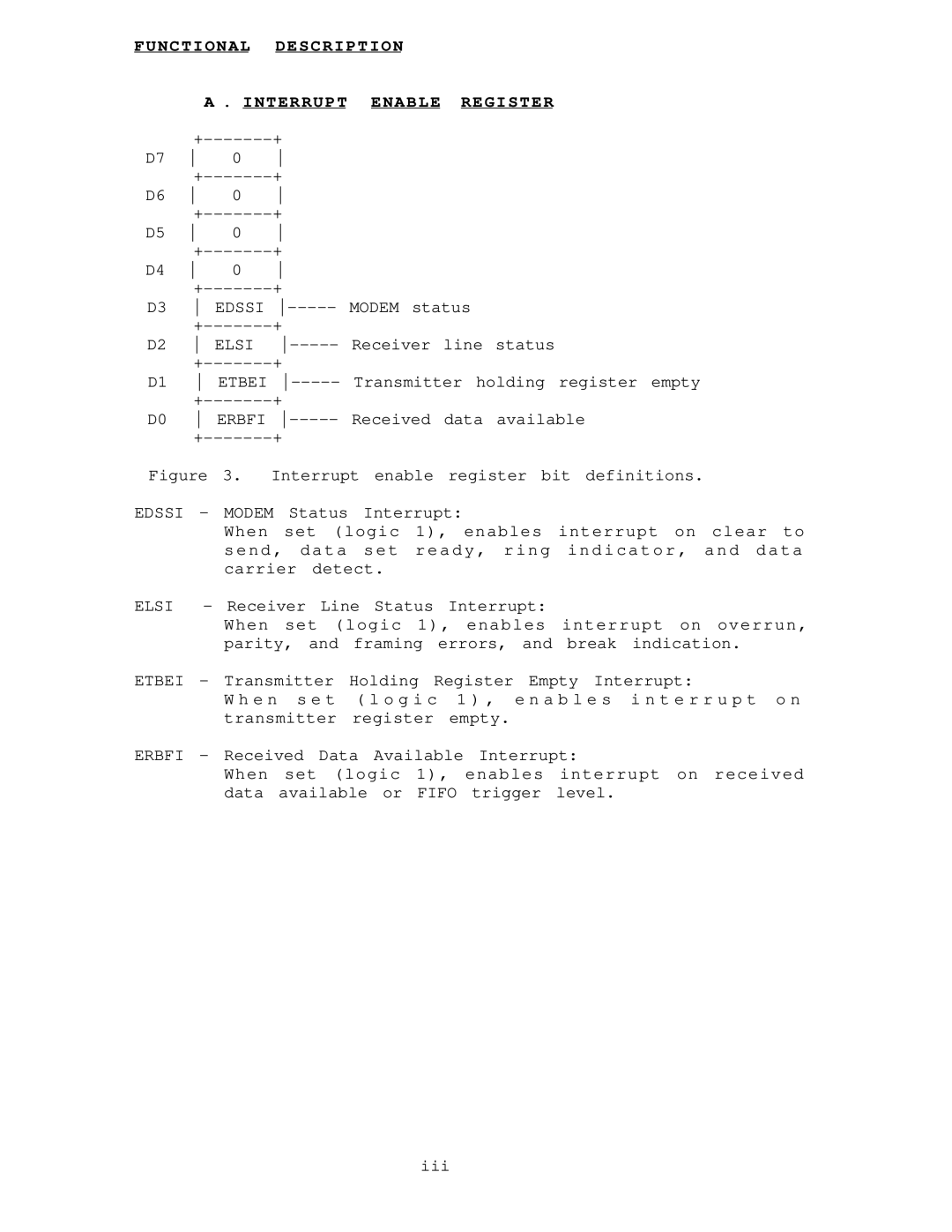

| A . INTERRUPT | ENABLE | REGISTER | |||

| + |

|

|

| ||

D7 | 0 |

|

|

| ||

| + |

|

|

| ||

D6 | 0 |

|

|

| ||

| + |

|

|

| ||

D5 | 0 |

|

|

| ||

| + |

|

|

| ||

D4 | 0 |

|

|

| ||

| + |

|

|

| ||

D3 | EDSSI | MODEM status | ||||

| + |

|

|

| ||

D2 | ELSI | Receiver | line status | |||

| + |

|

|

| ||

D1 | ETBEI | Transmitter holding register empty | ||||

| + |

|

|

| ||

D0 | ERBFI | Received | data available | |||

| + |

|

|

| ||

Figure 3. Interrupt enable register bit definitions. | ||||||

EDSSI | - | MODEM | Status | Interrupt: | ||

|

| When set (logic 1), enables interrupt on clear to | ||||

|

| send, data set ready, ring indicator, and data | ||||

|

| carrier | detect. |

| ||

ELSI | - | Receiver | Line Status | Interrupt: | ||

|

| When set (logic 1), enables interrupt on overrun, | ||||

|

| parity, and framing errors, and break indication. | ||||

ETBEI | - | Transmitter | Holding Register Empty Interrupt: | |||

|

| W h e n s e t ( l o g i c 1 ) , e n a b l e s i n t e r r u p t o n | ||||

|

| transmitter | register | empty. | ||

ERBFI | - | Received | Data Available Interrupt: | |||

|

| When set (logic 1), enables interrupt on received | ||||

|

| data | available or FIFO trigger level. | |||

iii