|

|

|

|

|

|

|

|

| FUNC |

|

|

| |

TIONAL | DESCRIPTION |

|

|

|

|

|

|

|

| ||||

+ |

|

|

|

|

| + |

| ||||||

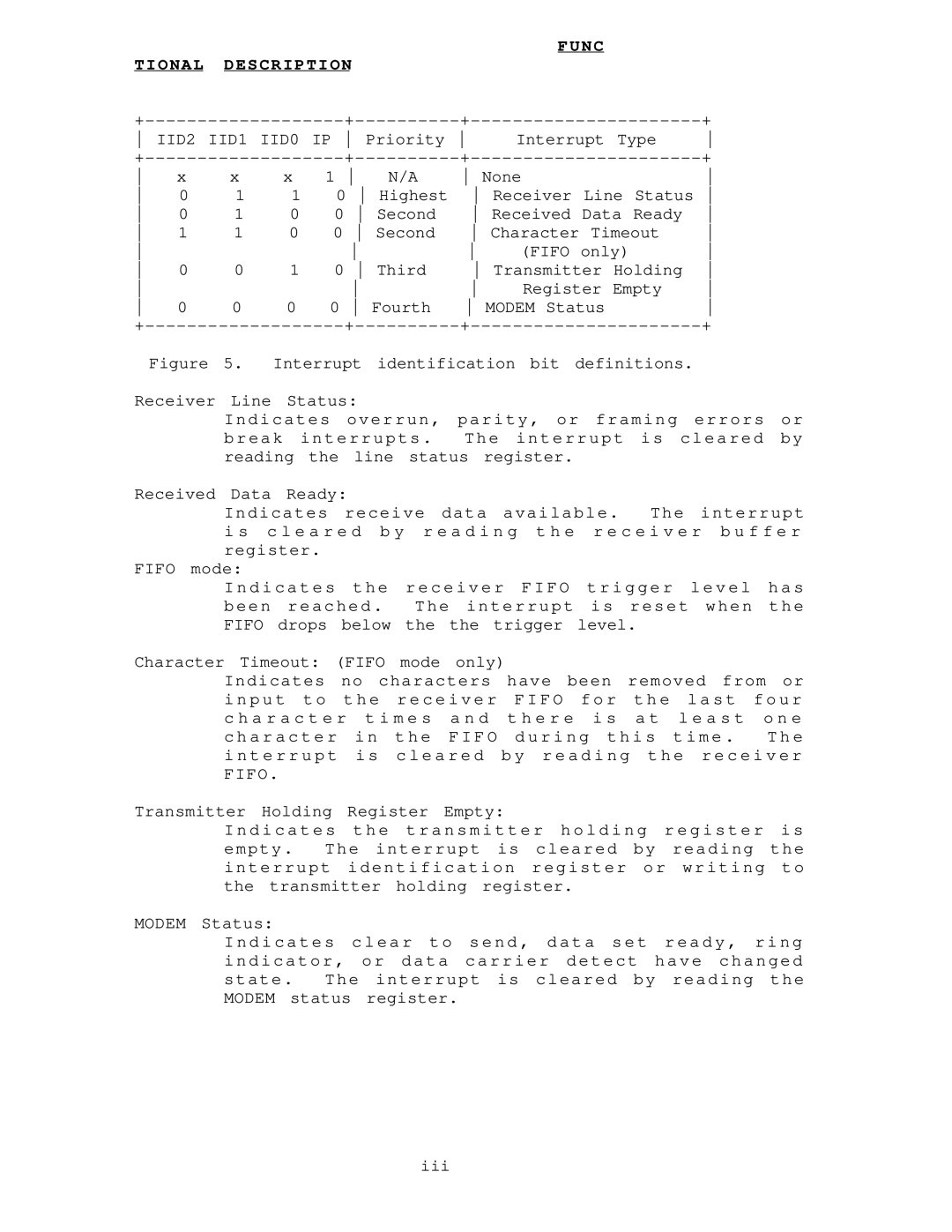

IID2 IID1 IID0 IP | Priority | Interrupt Type |

| ||||||||||

+ |

|

|

|

|

| + |

| ||||||

x | x | x | 1 |

| N/A | None |

|

|

| ||||

0 | 1 | 1 | 0 | Highest | Receiver | Line | Status |

| |||||

0 | 1 | 0 | 0 | Second | Received | Data | Ready |

| |||||

1 | 1 | 0 | 0 | Second | Character | Timeout |

| ||||||

|

|

|

|

| (FIFO only) |

| |||||||

0 | 0 | 1 | 0 | Third | Transmitter Holding |

| |||||||

|

|

|

|

| Register Empty |

| |||||||

0 | 0 | 0 | 0 | Fourth | MODEM Status |

|

| ||||||

+ |

|

|

|

|

| + |

| ||||||

| Figure 5. Interrupt identification bit definitions. |

|

| ||||||||||

Receiver | Line | Status: |

|

|

|

|

|

|

| ||||

|

| Indicates overrun, parity, or framing errors or | |||||||||||

|

| break interrupts . The interrupt is cleared by | |||||||||||

|

| reading the line status register. |

|

|

|

| |||||||

Received | Data | Ready: |

|

|

|

|

|

|

|

| |||

|

| Indicates | receive data | available. | The | interrupt | |||||||

|

| i s c l e a r e d b y r e a d i n g t h e r e c e i v e r b u f f e r | |||||||||||

|

| register. |

|

|

|

|

|

|

|

|

|

| |

FIFO mode: |

|

|

|

|

|

|

|

|

|

|

| ||

|

| I n d i c a t e s t h e r e c e i v e r F I F O t r i g g e r l e v e l h a s | |||||||||||

|

| been reached . The interrupt is reset when the | |||||||||||

|

| FIFO drops below the the trigger level. |

|

| |||||||||

Character Timeout: (FIFO mode | only) |

|

|

|

| ||||||||

|

| Indicates | no | characters have been | removed from | or | |||||||

|

| i n p u t t o t h e r e c e i v e r F I F O f o r t h e l a s t f o u r | |||||||||||

|

| c h a r a c t e r t i m e s a n d t h e r e i s a t l e a s t o n e | |||||||||||

|

| c h a r a c t e r i n t h e F I F O d u r i n g t h i s t i m e . | T h e | ||||||||||

|

| i n t e r r u p t i s c l e a r e d b y r e a d i n g t h e r e c e i v e r | |||||||||||

|

| FIFO. |

|

|

|

|

|

|

|

|

|

|

|

Transmitter Holding Register Empty:

I n d i c a t e s t h e t r a n s m i t t e r h o l d i n g r e g i s t e r i s empty. The interrupt is cleared by reading the interrupt identification register or writing to the transmitter holding register.

MODEM Status:

I n d i c a t e s c l e a r t o s e n d , d a t a s e t r e a d y , r i n g indicator, or data carrier detect have changed state. The interrupt is cleared by reading the MODEM status register.

iii