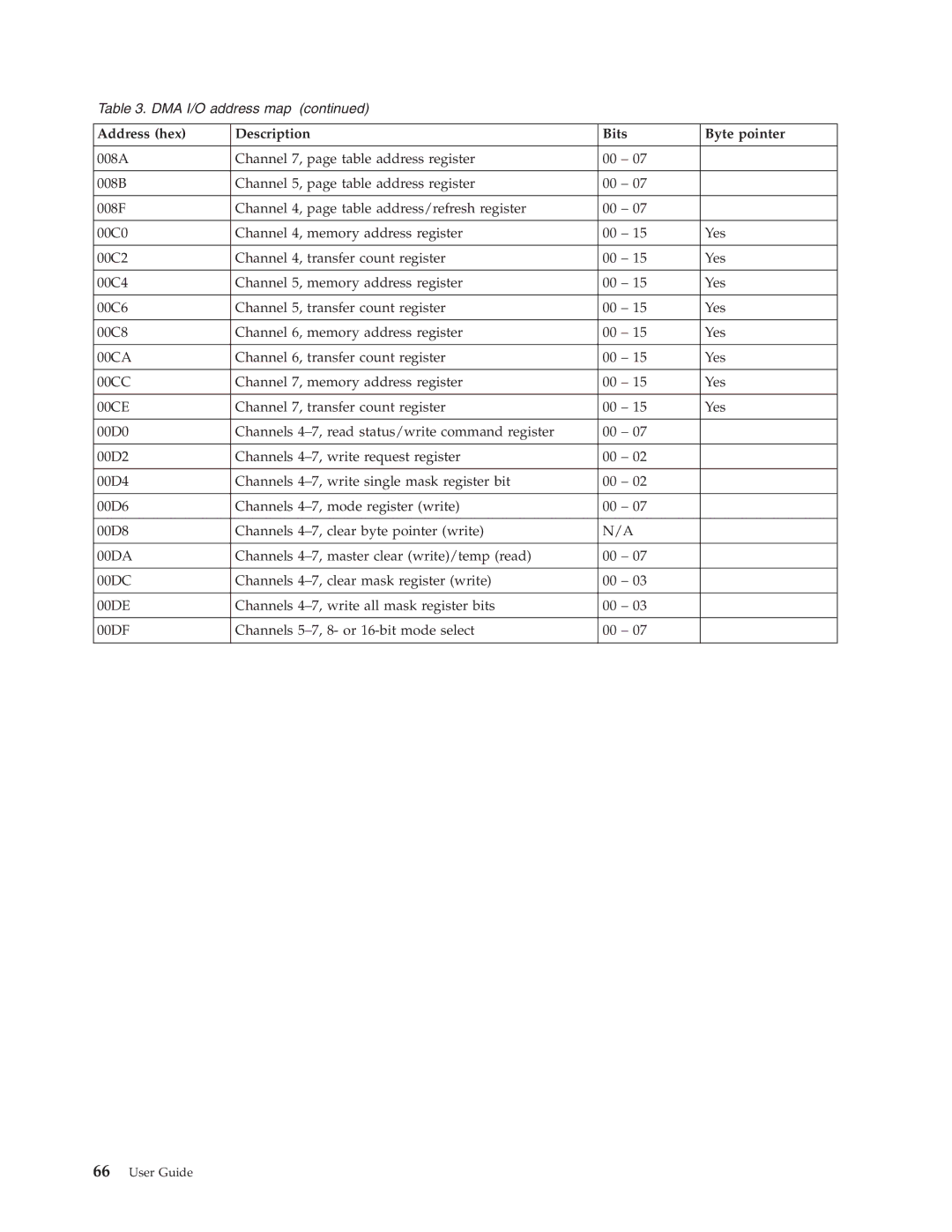

Table 3. DMA I/O address map (continued)

Address (hex) | Description | Bits | Byte pointer |

|

|

|

|

008A | Channel 7, page table address register | 00 – 07 |

|

|

|

|

|

008B | Channel 5, page table address register | 00 – 07 |

|

|

|

|

|

008F | Channel 4, page table address/refresh register | 00 – 07 |

|

|

|

|

|

00C0 | Channel 4, memory address register | 00 – 15 | Yes |

|

|

|

|

00C2 | Channel 4, transfer count register | 00 – 15 | Yes |

|

|

|

|

00C4 | Channel 5, memory address register | 00 – 15 | Yes |

|

|

|

|

00C6 | Channel 5, transfer count register | 00 – 15 | Yes |

|

|

|

|

00C8 | Channel 6, memory address register | 00 – 15 | Yes |

|

|

|

|

00CA | Channel 6, transfer count register | 00 – 15 | Yes |

|

|

|

|

00CC | Channel 7, memory address register | 00 – 15 | Yes |

|

|

|

|

00CE | Channel 7, transfer count register | 00 – 15 | Yes |

|

|

|

|

00D0 | Channels | 00 – 07 |

|

|

|

|

|

00D2 | Channels | 00 – 02 |

|

|

|

|

|

00D4 | Channels | 00 – 02 |

|

|

|

|

|

00D6 | Channels | 00 – 07 |

|

|

|

|

|

00D8 | Channels | N/A |

|

|

|

|

|

00DA | Channels | 00 – 07 |

|

|

|

|

|

00DC | Channels | 00 – 03 |

|

|

|

|

|

00DE | Channels | 00 – 03 |

|

|

|

|

|

00DF | Channels | 00 – 07 |

|

|

|

|

|