249323-003, Demo Board with FPGA for SS-SMII (Fiber)-to-MII Conversion specifications

The Intel 249323-003 demo board is an advanced platform designed for SS-SMII (Synchronous Serial - Synchronous Media Independent Interface) to MII (Media Independent Interface) conversion, utilizing FPGA technology. This demo board serves as a pivotal tool for developers and engineers in the field, facilitating the evaluation and testing of high-speed networking applications, particularly those involving fiber-optic communication.At its core, the Intel 249323-003 is equipped with a robust FPGA that is capable of handling complex data processing tasks with high efficiency. The FPGA architecture allows for flexible configuration, enabling users to customize the interface as per their specific application requirements. This adaptability is crucial in developing solutions for various networking protocols, ensuring seamless integration across different mediums.

One of the standout features of the demo board is its support for fiber-optic connections, which are essential for high-speed data transmission over long distances. The board includes interfaces that allow for the connection of fiber transceivers, thereby facilitating faster communication speeds and improved bandwidth efficiency. This capability is particularly beneficial for applications in data centers, telecommunications, and other high-bandwidth scenarios.

Additionally, the Intel 249323-003 demo board showcases low latency performance, a critical characteristic for real-time applications. This feature is achieved through sophisticated design and optimization techniques that ensure quick data processing. The board also supports various data rates, making it versatile enough for different use cases.

Another important aspect is the board’s power consumption efficiency. By implementing advanced power management techniques, the Intel 249323-003 minimizes energy usage while maximizing performance, making it a cost-effective solution for developers looking to create sustainable applications.

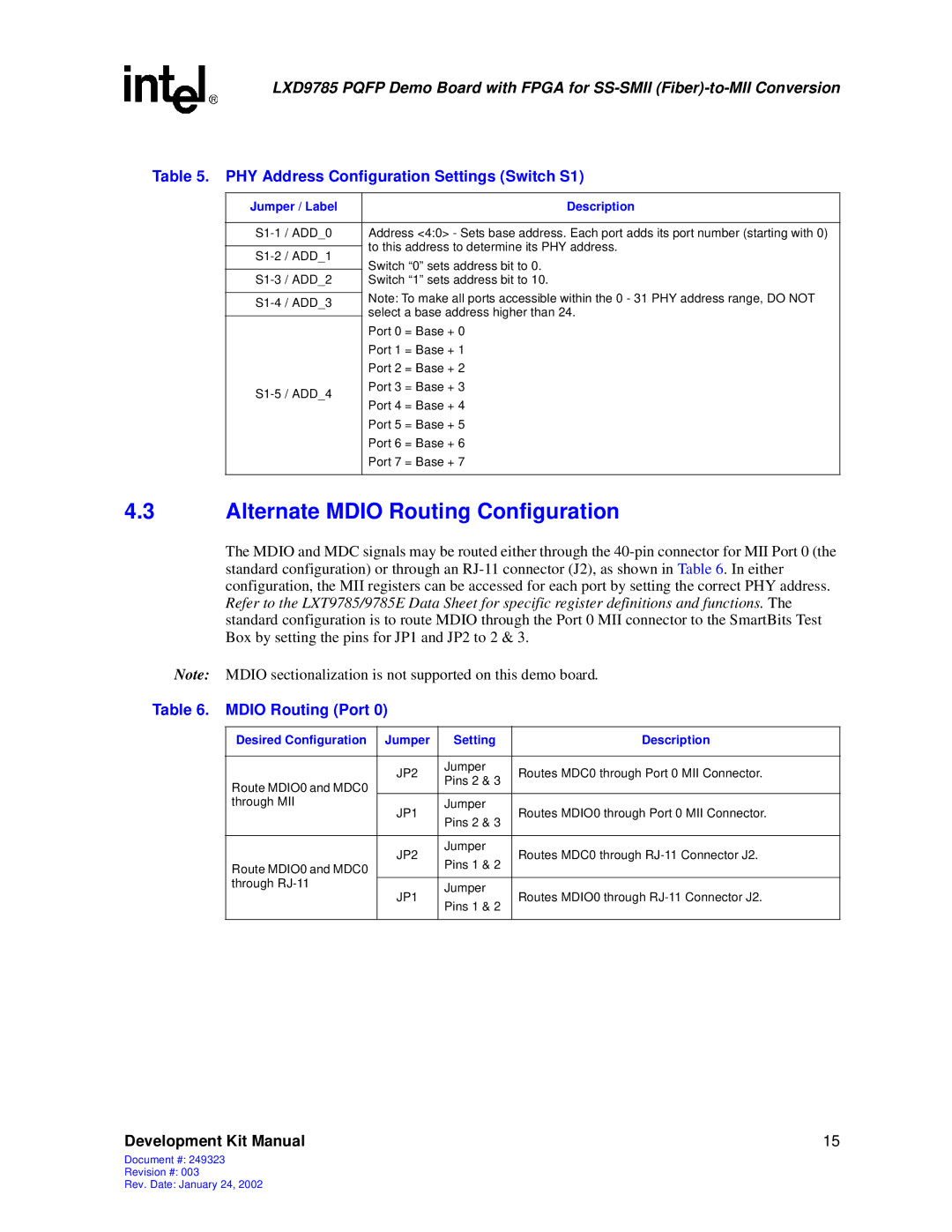

In terms of connectivity, the demo board offers multiple I/O options, facilitating interaction with other devices and systems. This eases the development process, allowing engineers to prototype and test their designs rapidly.

In conclusion, the Intel 249323-003 demo board is a sophisticated and versatile platform for SS-SMII to MII conversion. With its powerful FPGA, support for fiber-optic interfaces, low latency, and efficient power management, it stands out as a vital resource for developers working on high-speed networking solutions. Whether for prototyping or extensive testing, this demo board equips engineers with the tools necessary to innovate and elevate their networking projects to new heights.