User’s Manual ECB-865

FCC Statement

Disclaimer

Copyright Notice

Trademark Acknowledgement

Life Support Policy

Technical Support

Evalue Customer Services

Message to the Customer

Evalue Technology Inc Evalue Europe A/S

Product Warranty

Packing List

Watchdog Timer Programming Jumper & Connector

Manual Objectives Introduction

Connector Definitions

Setting Jumpers

Entering Setup

Map

Document Amendment History

Revision Date Comment

Manual Objectives

Introduction

System Overview

System Specifications

Chipset ITE IT8712F-A

Expansion Interface

Weight 0.5 Kg

Mechanical and Environmental

Architecture Overview

1 82815 Gmch and 82801BA

Multiplexed AGP and Display Cache Interface

Dram Interface

AGP Interface

6 USB

PCI Interface

Ethernet 7.1 ICH2 LAN Controller

ITE IT8712F-A

Intel

Systems DiskOnChip

Installation Procedure

Hardware Configuration

Safety Precautions

Removing CPU

Main Memory

Expansion Interface Installing the Single Board Computer

Installing DOC

Systems’ DiskOnChip Flash Disk

1 815E integrated Graphics Controller

Drivers Support

Disable WDT

Watchdog Timer Programming

Enable WDT

Re-trigger WDT

Jumper & Connector Jumper & Connector Layout

JP10

Jumper & Connector List

Jumpers Label Function

JP11

J11

Connectors Label Function

J10

J12

Setting Jumpers

Clear Cmos JP9

Watchdog Timer Enable / Disable Onboard Watchdog Timer JP12

Watchdog Timer Programming I/O Address Select JP6

0553H / 0033H 0543H / 0343H

JP10 16 Sec 32 Sec 64 Sec

Watchdog Timer Time-Out Interval Select JP10

Sec

10.3 COM2 RS-232/422/485 Select JP1, JP2~JP5

Proprietary PCI Bus Master Selection JP13

Systems DiskOnChip Memory Address Select JP11

Bus Master

Keyboard Lock & Power Indicator Connector J3

Connector Definitions System Reset Connector J1

External Speaker Connector J2

Primary IDE / Secondary IDE Active Indicator Connector J4

Primary IDE Connector J5

Secondary IDE Connector J10

ECB-865

Primary Master connector

STROBE, with the PIIX4 latching

RESET#

Floppy Connector J6

Signal Description Floppy Connector J6

DRVDEN0/1#

ATX Power Button Connector J8

Parallel Port Connector J11

11.12 DB25 Parallel Port Connector J11

Signal Description Parallel Port Connector J11

STB#

GND DTR CTS

CTS RTS DSR GND

CTS/RTS +

CPU Fan and System Fan Connector J14, J25

USB Connector J13, J19

Signal Description USB Connector J13, J19

Fast & Standard IrDA Connector J15

ATX Power Controller J16

Signal Configuration Fast & Standard IrDA Connector J15

Smart Card Interface J17

11.28 10/100 BASE-Tx Ethernet Connector J18, J20

Signal Description 10/100Base-Tx Ethernet Connector J18, J20

CRT Connector J22

Signal Description CRT Connector J22

Signal Description Int. & PS/2 Keyboard Connector J24, J26

Internal Keyboard Connector J24

11.33 PS/2 Keyboard Connector J26

11.35 PS/2 Mouse Connector J26

Proprietary PCI Connector J21

Write bursts

System

Interface Control

Error Reporting

Arbitration

Interrupts

AMI Bios Setup

Press F1 to Run Setup or Resume

AMI Bios Setup Main Menu

Enter key to accept or enter the sub-menu

Date and Time Configuration

Cmos Setup Reference Table

Standard Cmos Setup Menu

Floppy A, Floppy B

Boot Sector Virus Protection

Master Disk, Slave Disk

Advanced Cmos Setup Defaults

Quick Boot

BootUp Num-Lock

2.2 1st / 2nd / 3rd Boot Device

Try Other Boot Device

Password Check

System Bios Cacheable

Boot To OS/2

Shadow Memory from Address C000~DFFF, 16K Per Segment

ICH Delayed Transaction

Advanced Chipset Setup Defaults

CPU Ratio Selection

Memory Hole

Sdram RAS# to CAS# Delay

Internal Graphic Mode Select

Dram Cycle time SCLKs

Green PC Monitor Power State

Power Management Setup Defaults

Power Management/ APM

Acpi Aware O/S

Suspend Time Out Minute

CPU Critical Temperature

Stand by Time Out Minute

Throttle Slow Clock Ratio

Wake Up on Ring

Power Button Function

Wake Up on LAN

PCI / Plug and Play Setup Defaults

Plug and Play Aware O/S

PCI / VGA Palette Snoop

PCI Latency Timer PCI Clocks

Clear Nvram

Allocate IRQ to PCI VGA

OnBoard Serial Port1

Peripheral Setup Defaults

OnBoard FDC

OnBoard Serial Port2

On Board Parallel Port

Disabled

Parallel Port Mode

378h

Parallel Port DMA Channel

Parallel Port IRQ

On-Chip IDE

Hardware Monitor Setup Defaults

User’s Manual

Driver Installation

Driver Installation for Ethernet Adapter Windows

User’s Manual

ECB-865

User’s Manual

ECB-865

Windows NT 4.0 Ethernet Installation

ECB-865

User’s Manual

ECB-865

User’s Manual

Driver Installation for Display Adapter Windows

User’s Manual

ECB-865

User’s Manual

ECB-865

Windows NT 4.0 Display Installation

ECB-865

User’s Manual

ECB-865

Measurement Drawing

Appendix a Bios Revisions

Bios Rev New Features Bugs/Problems Solved Known Problems

Appendix B System Resources

Memory Map

Map

Port Description

User’s Manual

Interrupt Usage

Interrupt Description

DMA-channel Usage

DMA-channel Description

Appendix C Amibios Power-On Self Test

If it beeps… Then…

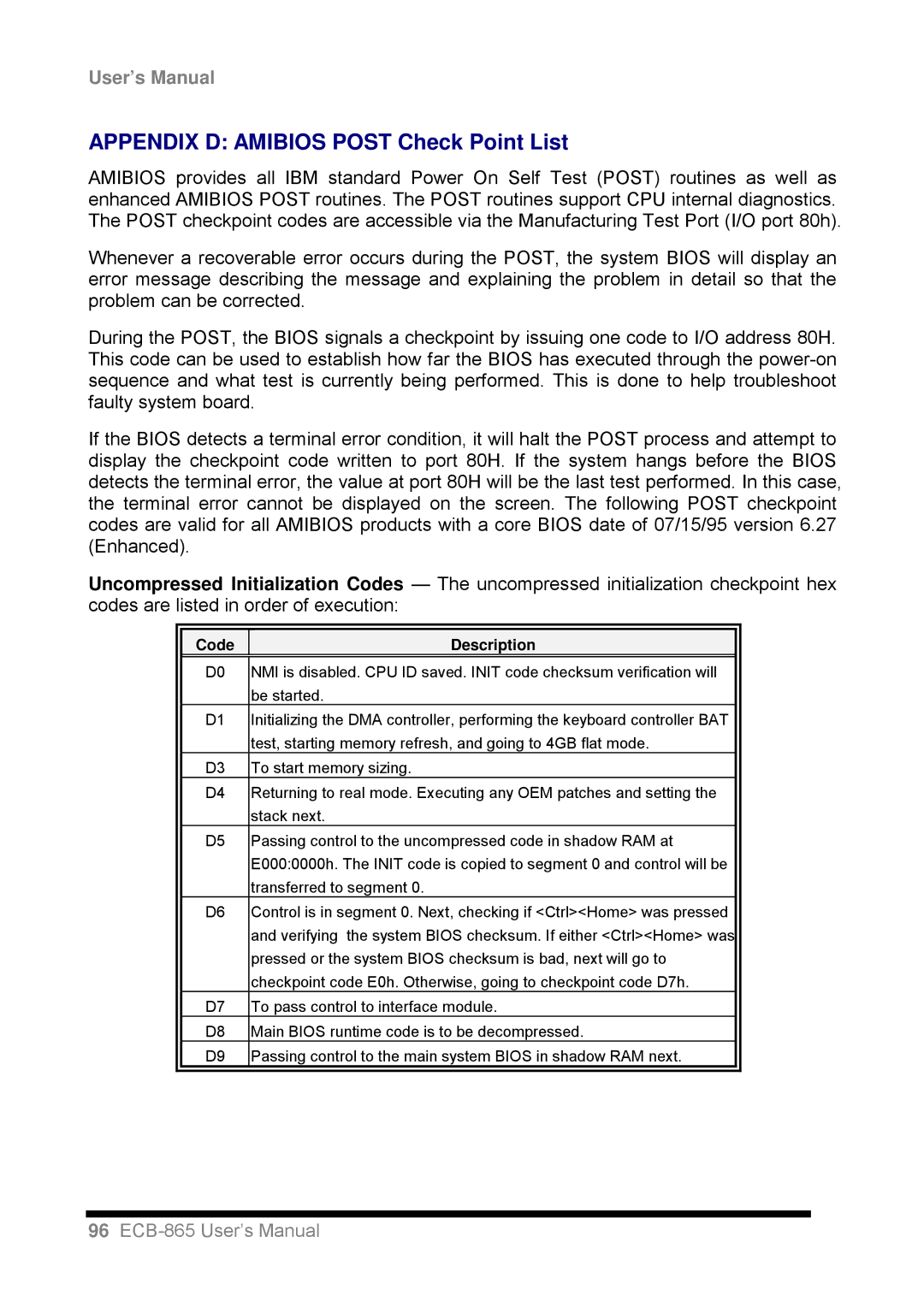

Appendix D Amibios Post Check Point List

Code Description

Bios

User’s Manual

Present

User’s Manual

ECB-865

User’s Manual