ECB-865

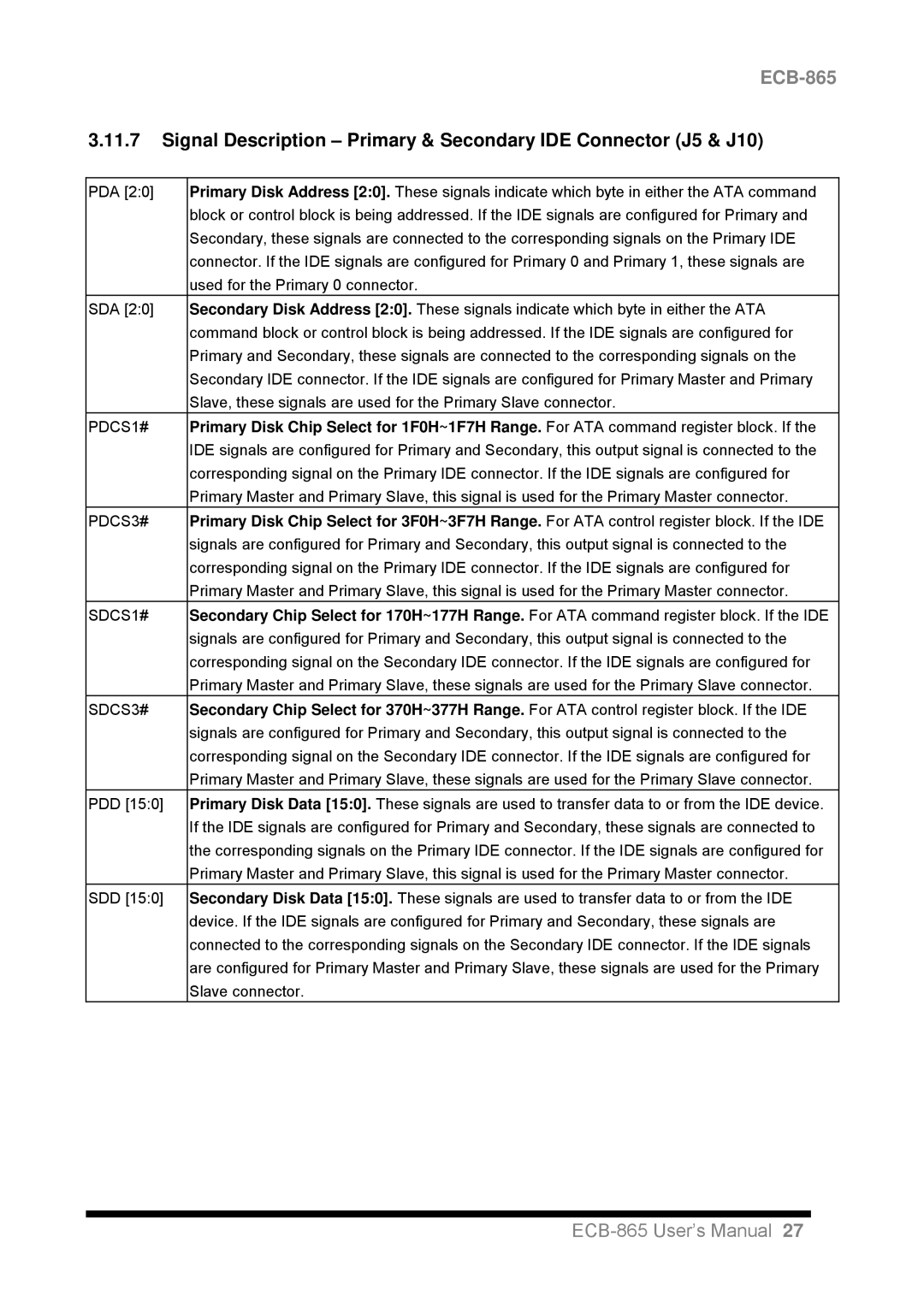

3.11.7Signal Description – Primary & Secondary IDE Connector (J5 & J10)

PDA [2:0] | Primary Disk Address [2:0]. These signals indicate which byte in either the ATA command |

| block or control block is being addressed. If the IDE signals are configured for Primary and |

| Secondary, these signals are connected to the corresponding signals on the Primary IDE |

| connector. If the IDE signals are configured for Primary 0 and Primary 1, these signals are |

| used for the Primary 0 connector. |

SDA [2:0] | Secondary Disk Address [2:0]. These signals indicate which byte in either the ATA |

| command block or control block is being addressed. If the IDE signals are configured for |

| Primary and Secondary, these signals are connected to the corresponding signals on the |

| Secondary IDE connector. If the IDE signals are configured for Primary Master and Primary |

| Slave, these signals are used for the Primary Slave connector. |

PDCS1# | Primary Disk Chip Select for 1F0H~1F7H Range. For ATA command register block. If the |

| IDE signals are configured for Primary and Secondary, this output signal is connected to the |

| corresponding signal on the Primary IDE connector. If the IDE signals are configured for |

| Primary Master and Primary Slave, this signal is used for the Primary Master connector. |

PDCS3# | Primary Disk Chip Select for 3F0H~3F7H Range. For ATA control register block. If the IDE |

| signals are configured for Primary and Secondary, this output signal is connected to the |

| corresponding signal on the Primary IDE connector. If the IDE signals are configured for |

| Primary Master and Primary Slave, this signal is used for the Primary Master connector. |

SDCS1# | Secondary Chip Select for 170H~177H Range. For ATA command register block. If the IDE |

| signals are configured for Primary and Secondary, this output signal is connected to the |

| corresponding signal on the Secondary IDE connector. If the IDE signals are configured for |

| Primary Master and Primary Slave, these signals are used for the Primary Slave connector. |

SDCS3# | Secondary Chip Select for 370H~377H Range. For ATA control register block. If the IDE |

| signals are configured for Primary and Secondary, this output signal is connected to the |

| corresponding signal on the Secondary IDE connector. If the IDE signals are configured for |

| Primary Master and Primary Slave, these signals are used for the Primary Slave connector. |

PDD [15:0] | Primary Disk Data [15:0]. These signals are used to transfer data to or from the IDE device. |

| If the IDE signals are configured for Primary and Secondary, these signals are connected to |

| the corresponding signals on the Primary IDE connector. If the IDE signals are configured for |

| Primary Master and Primary Slave, this signal is used for the Primary Master connector. |

SDD [15:0] | Secondary Disk Data [15:0]. These signals are used to transfer data to or from the IDE |

| device. If the IDE signals are configured for Primary and Secondary, these signals are |

| connected to the corresponding signals on the Secondary IDE connector. If the IDE signals |

| are configured for Primary Master and Primary Slave, these signals are used for the Primary |

| Slave connector. |