|

|

|

|

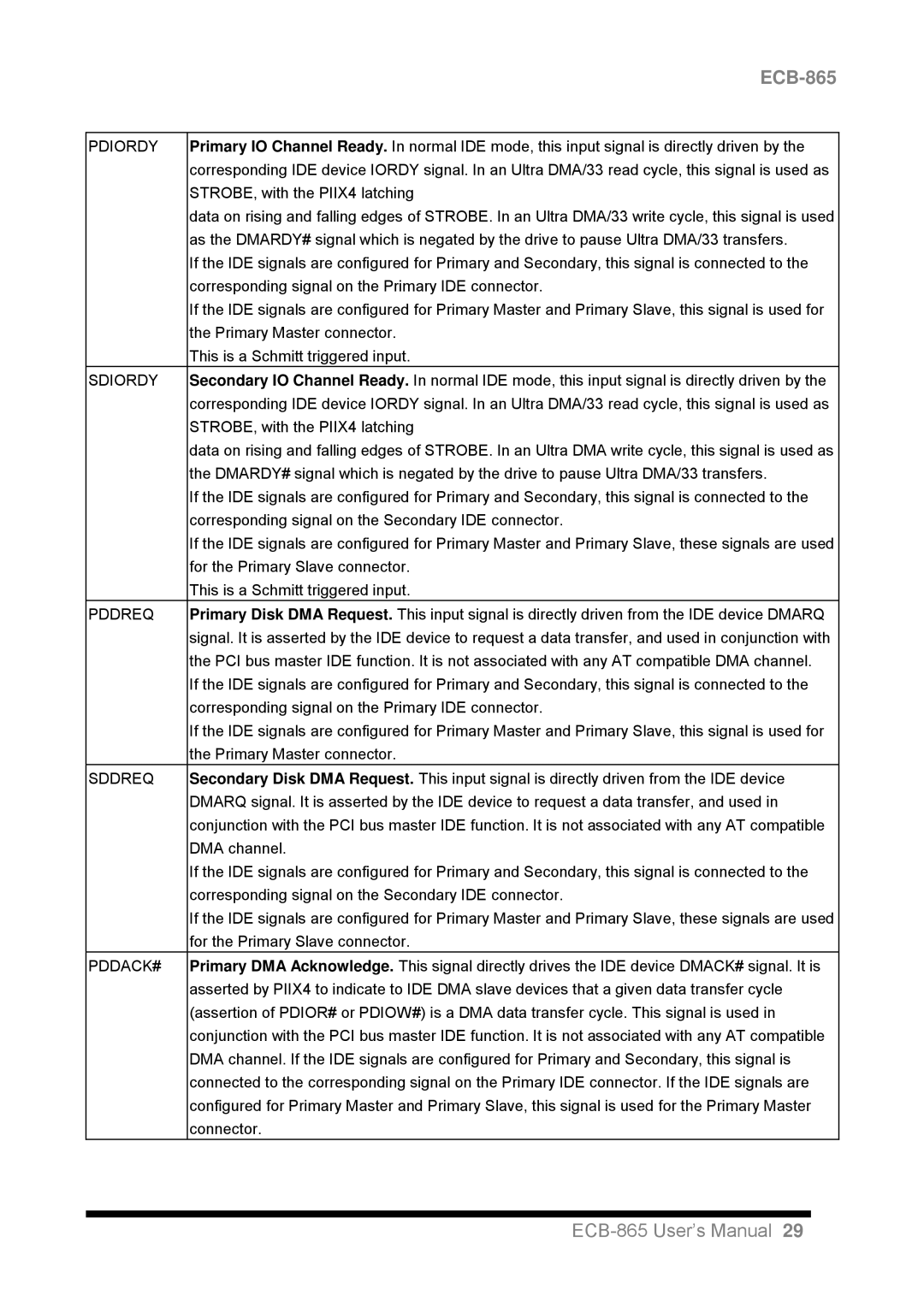

PDIORDY | Primary IO Channel Ready. In normal IDE mode, this input signal is directly driven by the |

| corresponding IDE device IORDY signal. In an Ultra DMA/33 read cycle, this signal is used as |

| STROBE, with the PIIX4 latching |

| data on rising and falling edges of STROBE. In an Ultra DMA/33 write cycle, this signal is used |

| as the DMARDY# signal which is negated by the drive to pause Ultra DMA/33 transfers. |

| If the IDE signals are configured for Primary and Secondary, this signal is connected to the |

| corresponding signal on the Primary IDE connector. |

| If the IDE signals are configured for Primary Master and Primary Slave, this signal is used for |

| the Primary Master connector. |

| This is a Schmitt triggered input. |

SDIORDY | Secondary IO Channel Ready. In normal IDE mode, this input signal is directly driven by the |

| corresponding IDE device IORDY signal. In an Ultra DMA/33 read cycle, this signal is used as |

| STROBE, with the PIIX4 latching |

| data on rising and falling edges of STROBE. In an Ultra DMA write cycle, this signal is used as |

| the DMARDY# signal which is negated by the drive to pause Ultra DMA/33 transfers. |

| If the IDE signals are configured for Primary and Secondary, this signal is connected to the |

| corresponding signal on the Secondary IDE connector. |

| If the IDE signals are configured for Primary Master and Primary Slave, these signals are used |

| for the Primary Slave connector. |

| This is a Schmitt triggered input. |

PDDREQ | Primary Disk DMA Request. This input signal is directly driven from the IDE device DMARQ |

| signal. It is asserted by the IDE device to request a data transfer, and used in conjunction with |

| the PCI bus master IDE function. It is not associated with any AT compatible DMA channel. |

| If the IDE signals are configured for Primary and Secondary, this signal is connected to the |

| corresponding signal on the Primary IDE connector. |

| If the IDE signals are configured for Primary Master and Primary Slave, this signal is used for |

| the Primary Master connector. |

SDDREQ | Secondary Disk DMA Request. This input signal is directly driven from the IDE device |

| DMARQ signal. It is asserted by the IDE device to request a data transfer, and used in |

| conjunction with the PCI bus master IDE function. It is not associated with any AT compatible |

| DMA channel. |

| If the IDE signals are configured for Primary and Secondary, this signal is connected to the |

| corresponding signal on the Secondary IDE connector. |

| If the IDE signals are configured for Primary Master and Primary Slave, these signals are used |

| for the Primary Slave connector. |

PDDACK# | Primary DMA Acknowledge. This signal directly drives the IDE device DMACK# signal. It is |

| asserted by PIIX4 to indicate to IDE DMA slave devices that a given data transfer cycle |

| (assertion of PDIOR# or PDIOW#) is a DMA data transfer cycle. This signal is used in |

| conjunction with the PCI bus master IDE function. It is not associated with any AT compatible |

| DMA channel. If the IDE signals are configured for Primary and Secondary, this signal is |

| connected to the corresponding signal on the Primary IDE connector. If the IDE signals are |

| configured for Primary Master and Primary Slave, this signal is used for the Primary Master |

| connector. |