ECB-865

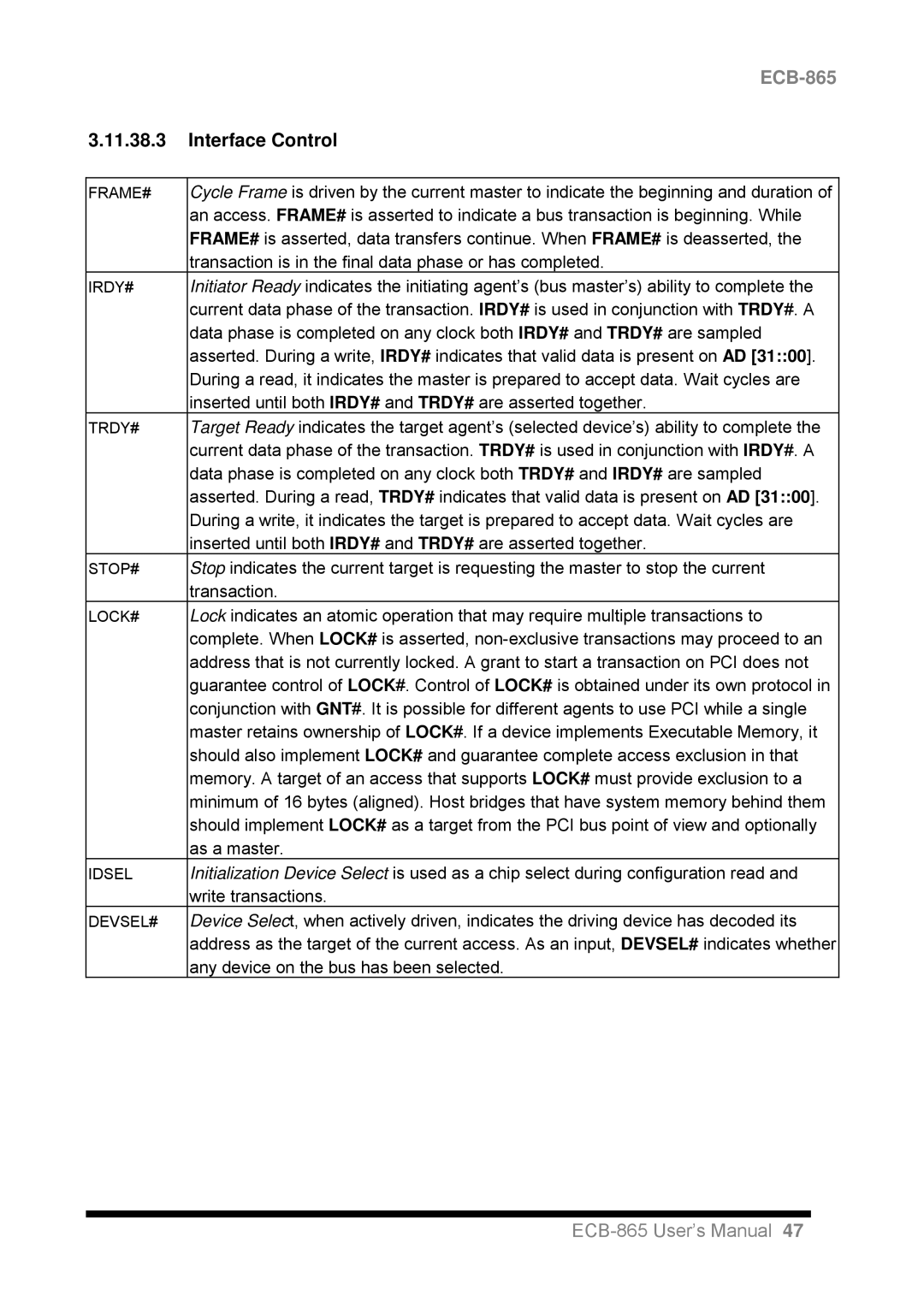

3.11.38.3Interface Control

FRAME# | Cycle Frame is driven by the current master to indicate the beginning and duration of |

| an access. FRAME# is asserted to indicate a bus transaction is beginning. While |

| FRAME# is asserted, data transfers continue. When FRAME# is deasserted, the |

| transaction is in the final data phase or has completed. |

IRDY# | Initiator Ready indicates the initiating agent’s (bus master’s) ability to complete the |

| current data phase of the transaction. IRDY# is used in conjunction with TRDY#. A |

| data phase is completed on any clock both IRDY# and TRDY# are sampled |

| asserted. During a write, IRDY# indicates that valid data is present on AD [31::00]. |

| During a read, it indicates the master is prepared to accept data. Wait cycles are |

| inserted until both IRDY# and TRDY# are asserted together. |

TRDY# | Target Ready indicates the target agent’s (selected device’s) ability to complete the |

| current data phase of the transaction. TRDY# is used in conjunction with IRDY#. A |

| data phase is completed on any clock both TRDY# and IRDY# are sampled |

| asserted. During a read, TRDY# indicates that valid data is present on AD [31::00]. |

| During a write, it indicates the target is prepared to accept data. Wait cycles are |

| inserted until both IRDY# and TRDY# are asserted together. |

STOP# | Stop indicates the current target is requesting the master to stop the current |

| transaction. |

LOCK# | Lock indicates an atomic operation that may require multiple transactions to |

| complete. When LOCK# is asserted, |

| address that is not currently locked. A grant to start a transaction on PCI does not |

| guarantee control of LOCK#. Control of LOCK# is obtained under its own protocol in |

| conjunction with GNT#. It is possible for different agents to use PCI while a single |

| master retains ownership of LOCK#. If a device implements Executable Memory, it |

| should also implement LOCK# and guarantee complete access exclusion in that |

| memory. A target of an access that supports LOCK# must provide exclusion to a |

| minimum of 16 bytes (aligned). Host bridges that have system memory behind them |

| should implement LOCK# as a target from the PCI bus point of view and optionally |

| as a master. |

IDSEL | Initialization Device Select is used as a chip select during configuration read and |

| write transactions. |

DEVSEL# | Device Select, when actively driven, indicates the driving device has decoded its |

| address as the target of the current access. As an input, DEVSEL# indicates whether |

| any device on the bus has been selected. |