UPI-C42/UPI-L42

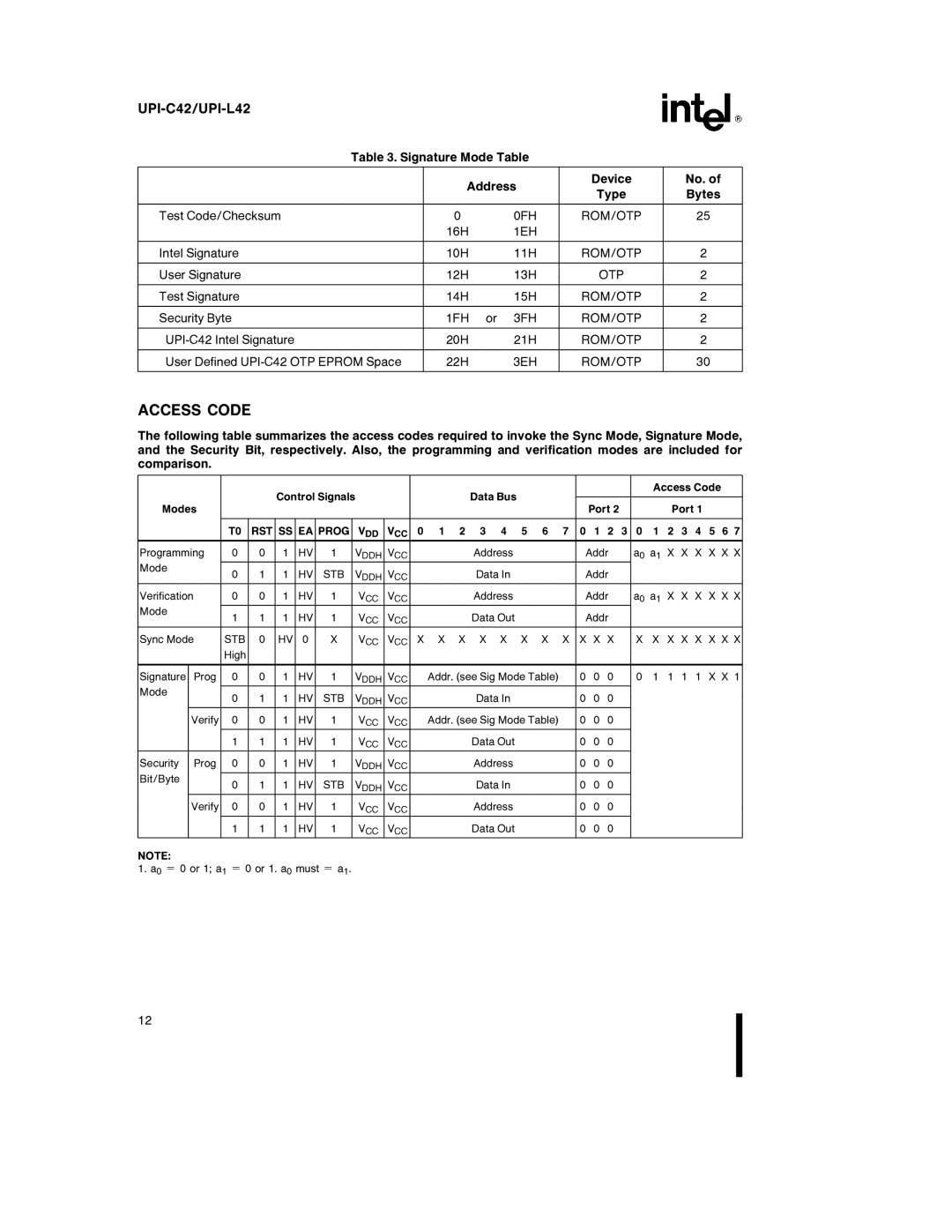

Table 3. Signature Mode Table

| Address | Device | No. of | |

| Type | Bytes | ||

|

|

| ||

|

|

|

|

|

Test Code/Checksum | 0 | 0FH | ROM/OTP | 25 |

| 16H | 1EH |

|

|

|

|

|

|

|

Intel Signature | 10H | 11H | ROM/OTP | 2 |

|

|

|

|

|

User Signature | 12H | 13H | OTP | 2 |

|

|

|

|

|

Test Signature | 14H | 15H | ROM/OTP | 2 |

|

|

|

|

|

Security Byte | 1FH | or 3FH | ROM/OTP | 2 |

|

|

|

|

|

20H | 21H | ROM/OTP | 2 | |

|

|

|

|

|

User Defined | 22H | 3EH | ROM/OTP | 30 |

|

|

|

|

|

ACCESS CODE

The following table summarizes the access codes required to invoke the Sync Mode, Signature Mode, and the Security Bit, respectively. Also, the programming and verification modes are included for comparison.

|

|

|

| Control Signals |

|

|

|

| Data Bus |

|

|

|

|

|

|

|

| Access Code | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

Modes |

|

|

|

|

|

|

|

|

|

| Port 2 |

|

|

| Port 1 |

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| T0 | RST | SS | EA | PROG | VDD | VCC | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 0 | 1 | 2 | 3 | 4 | 5 6 7 |

Programming | 0 | 0 | 1 | HV | 1 | VDDH | VCC |

|

|

| Address |

|

|

| Addr |

| a0 a1 X | X | X | X X X | ||||||

Mode |

| 0 | 1 | 1 | HV | STB | VDDH | VCC |

|

|

| Data In |

|

|

| Addr |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

Verification | 0 | 0 | 1 | HV | 1 | VCC | VCC |

|

|

| Address |

|

|

| Addr |

| a0 a1 X | X | X | X X X | ||||||

Mode |

| 1 | 1 | 1 | HV | 1 | VCC | VCC |

|

|

| Data Out |

|

|

| Addr |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

Sync Mode | STB | 0 | HV | 0 | X | VCC | VCC | X | X | X | X | X | X | X | X | X X X |

| X | X | X X X X X X | ||||||

|

| High |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

Signature | Prog | 0 | 0 | 1 | HV | 1 | VDDH | VCC |

| Addr. (see Sig Mode Table) |

| 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | X X 1 | |||||

Mode |

| 0 | 1 | 1 | HV | STB | VDDH | VCC |

|

|

| Data In |

|

|

| 0 | 0 | 0 |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

| Verify | 0 | 0 | 1 | HV | 1 | VCC | VCC |

| Addr. (see Sig Mode Table) |

| 0 | 0 | 0 |

|

|

|

|

|

|

| |||||

|

| 1 | 1 | 1 | HV | 1 | VCC | VCC |

|

|

| Data Out |

|

|

| 0 | 0 | 0 |

|

|

|

|

|

|

| |

Security | Prog | 0 | 0 | 1 | HV | 1 | VDDH | VCC |

|

|

| Address |

|

|

| 0 | 0 | 0 |

|

|

|

|

|

|

| |

Bit/Byte |

| 0 | 1 | 1 | HV | STB | VDDH | VCC |

|

|

| Data In |

|

|

| 0 | 0 | 0 |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

| Verify | 0 | 0 | 1 | HV | 1 | VCC | VCC |

|

|

| Address |

|

|

| 0 | 0 | 0 |

|

|

|

|

|

|

| |

|

| 1 | 1 | 1 | HV | 1 | VCC | VCC |

|

|

| Data Out |

|

|

| 0 | 0 | 0 |

|

|

|

|

|

|

| |

NOTE:

1. a0 e 0 or 1; a1 e 0 or 1. a0 must e a1.

12