UPI-C42/UPI-L42

If ‘‘EN DMA’’ has been executed, P27 becomes the DACK (DMA ACKnowledge) pin. This pin acts as a chip select input for the Data Bus Buffer registers during DMA transfers.

EN DMA | Op Code: 0E5H |

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

1 |

| 1 | 1 | 0 |

| 0 | 1 | 0 | 1 |

|

|

|

|

|

|

|

|

|

|

D7 |

|

|

|

|

|

|

| D0 | |

6.When EA is enabled on the UPI, the program counter is placed on Port 1 and the lower four

bits of Port 2 (MSB e P23, LSB e P10). On the UPI this information is multiplexed with PORT DATA (see port timing diagrams at end of this data sheet).

7.The

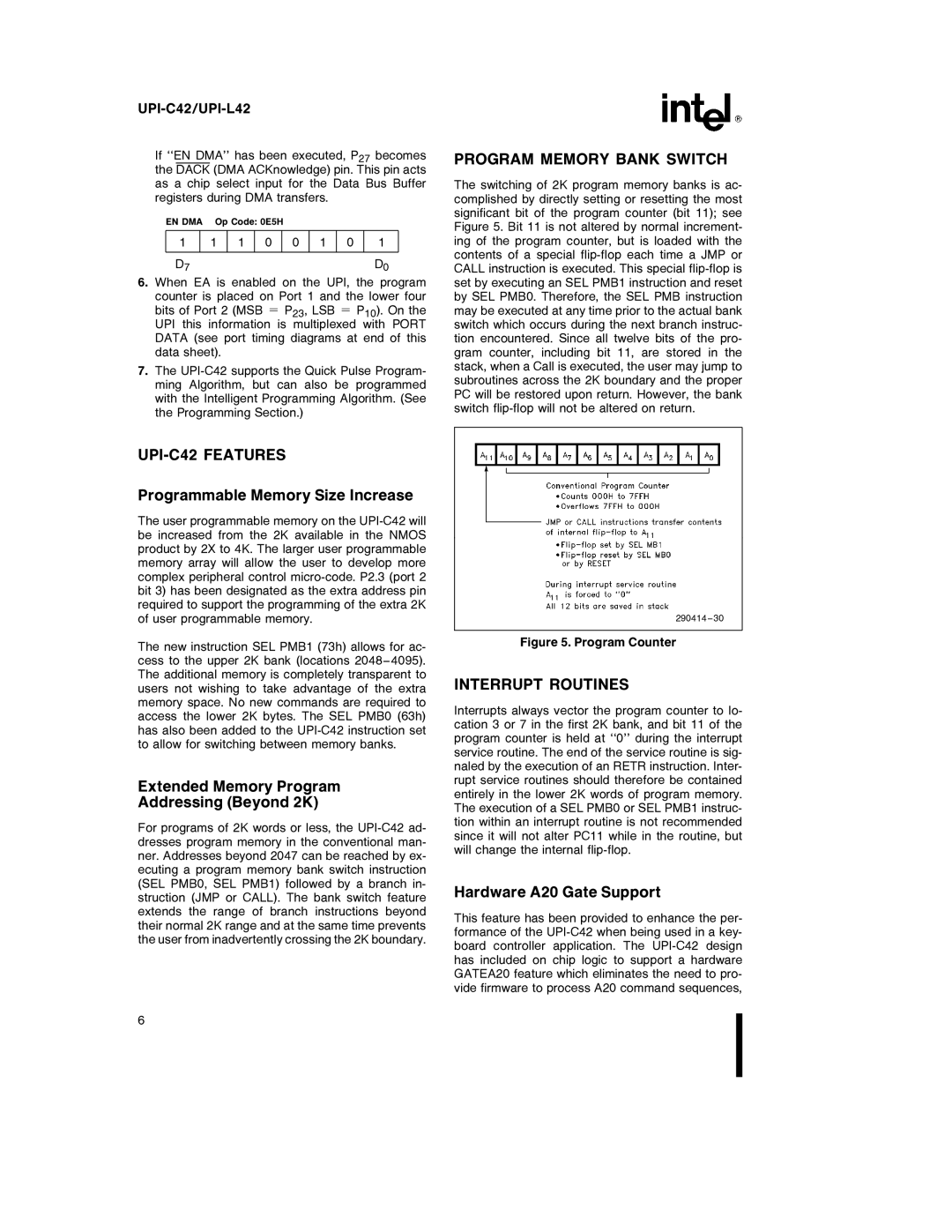

PROGRAM MEMORY BANK SWITCH

The switching of 2K program memory banks is ac- complished by directly setting or resetting the most significant bit of the program counter (bit 11); see Figure 5. Bit 11 is not altered by normal increment- ing of the program counter, but is loaded with the contents of a special

UPI-C42 FEATURES

Programmable Memory Size Increase

The user programmable memory on the

The new instruction SEL PMB1 (73h) allows for ac- cess to the upper 2K bank (locations 2048 – 4095). The additional memory is completely transparent to users not wishing to take advantage of the extra memory space. No new commands are required to access the lower 2K bytes. The SEL PMB0 (63h) has also been added to the

Extended Memory Program

Addressing (Beyond 2K)

For programs of 2K words or less, the

290414 – 30

Figure 5. Program Counter

INTERRUPT ROUTINES

Interrupts always vector the program counter to lo- cation 3 or 7 in the first 2K bank, and bit 11 of the program counter is held at ‘‘0’’ during the interrupt service routine. The end of the service routine is sig- naled by the execution of an RETR instruction. Inter- rupt service routines should therefore be contained entirely in the lower 2K words of program memory. The execution of a SEL PMB0 or SEL PMB1 instruc- tion within an interrupt routine is not recommended since it will not alter PC11 while in the routine, but will change the internal

Hardware A20 Gate Support

This feature has been provided to enhance the per- formance of the

6