This circuitry gives the host direct control of port 2 bit 1 (P2.1) without intervention by the internal CPU. When this opcode is executed, P2.1 becomes a ded- icated output pin. The status of this pin is

SUSPEND Invoke Suspend Power Down Mode

OPCODE 1000 0010 (82h) or 1110 0010 (E2h)

Enables device to enter micro power mode. In this mode the external oscillator is off, CPU operation is stopped, and the Port pins are tristated. This mode can only be exited via a RESET signal.

PROGRAMMING AND VERIFYING THE UPI-C42

The

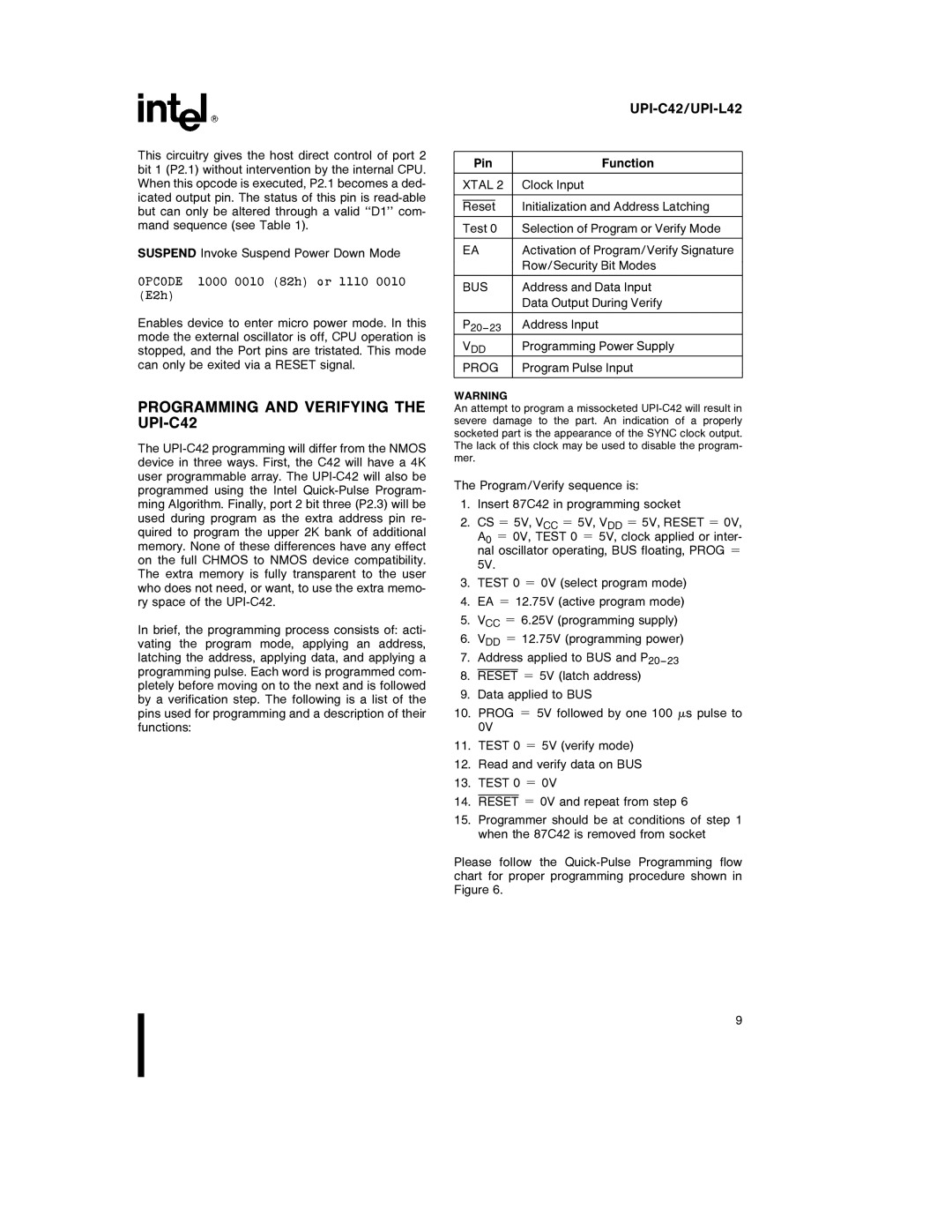

In brief, the programming process consists of: acti- vating the program mode, applying an address, latching the address, applying data, and applying a programming pulse. Each word is programmed com- pletely before moving on to the next and is followed by a verification step. The following is a list of the pins used for programming and a description of their functions:

|

|

|

|

|

|

|

|

| Pin | Function | |

|

|

|

|

| XTAL 2 | Clock Input | |

|

|

|

|

|

|

|

|

| Reset | Initialization and Address Latching | |

|

|

| |

| Test 0 | Selection of Program or Verify Mode | |

|

|

| |

| EA | Activation of Program/Verify Signature | |

|

|

| Row/Security Bit Modes |

|

|

| |

| BUS | Address and Data Input | |

|

|

| Data Output During Verify |

|

|

| |

| P20 – 23 | Address Input | |

| VDD | Programming Power Supply | |

| PROG | Program Pulse Input | |

|

|

|

|

WARNING

An attempt to program a missocketed

The Program/Verify sequence is:

1.Insert 87C42 in programming socket

2.CS e 5V, VCC e 5V, VDD e 5V, RESET e 0V, A0 e 0V, TEST 0 e 5V, clock applied or inter- nal oscillator operating, BUS floating, PROG e 5V.

3.TEST 0 e 0V (select program mode)

4.EA e 12.75V (active program mode)

5.VCC e 6.25V (programming supply)

6.VDD e 12.75V (programming power)

7.Address applied to BUS and P20 – 23

8.RESET e 5V (latch address)

9.Data applied to BUS

10.PROG e 5V followed by one 100 ms pulse to 0V

11.TEST 0 e 5V (verify mode)

12.Read and verify data on BUS

13.TEST 0 e 0V

14.RESET e 0V and repeat from step 6

15.Programmer should be at conditions of step 1 when the 87C42 is removed from socket

Please follow the

9