Page 30

Model: |

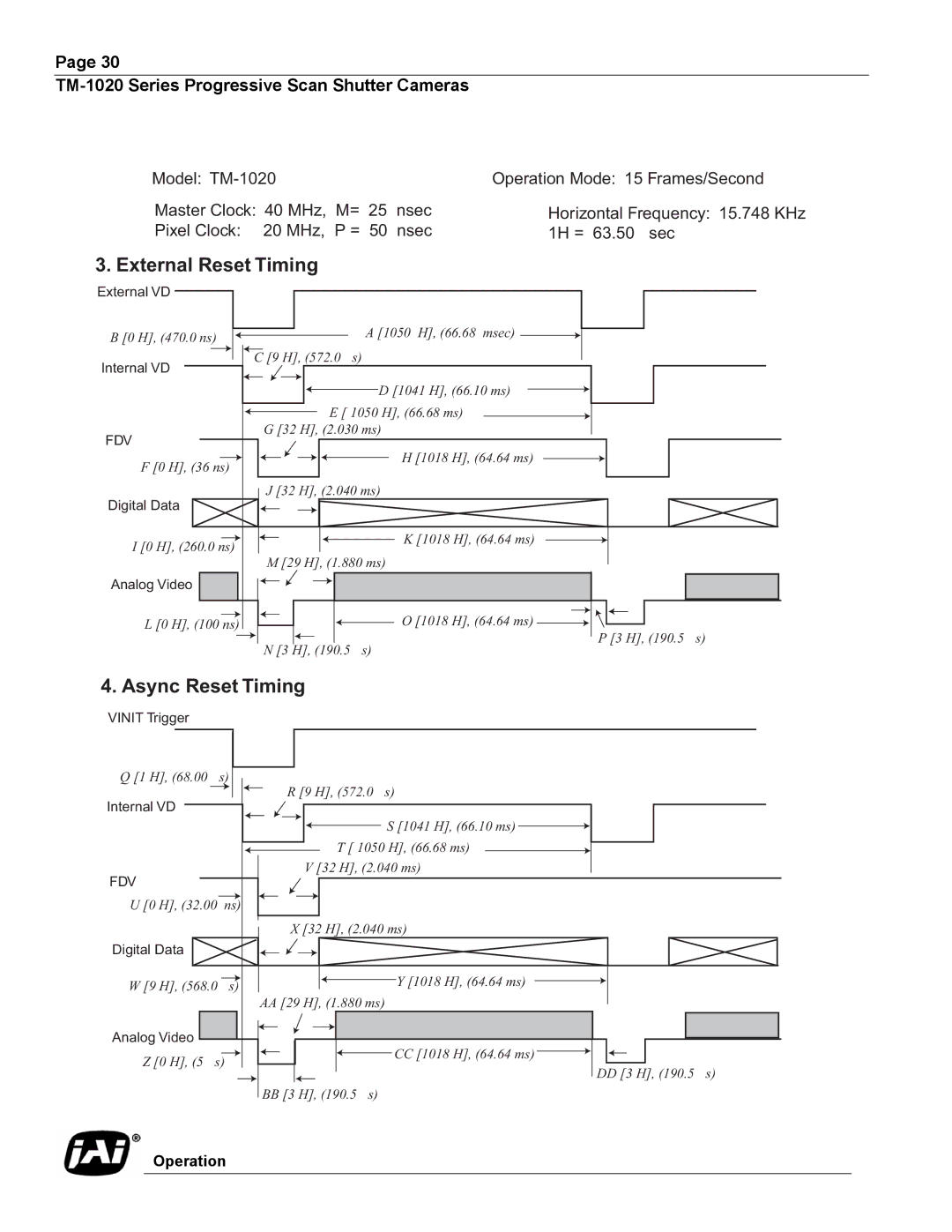

| Operation Mode: 15 Frames/Second |

Master Clock: 40 MHz, M= 25 | nsec | Horizontal Frequency: 15.748 KHz |

Pixel Clock: 20 MHz, P = 50 | nsec | 1H = 63.50 sec |

3. External Reset Timing

External VD

B [0 H], (470.0 ns) | A [1050 H], (66.68 msec) |

|

|

| |

C [9 H], (572.0 | s) |

|

Internal VD |

|

|

| D [1041 H], (66.10 ms) |

|

E [ 1050 H], (66.68 ms) |

| |

G [32 H], (2.030 ms) |

| |

FDV |

|

|

F [0 H], (36 ns) | H [1018 H], (64.64 ms) |

|

|

| |

J [32 H], (2.040 ms) |

| |

Digital Data |

|

|

I [0 H], (260.0 ns) | K [1018 H], (64.64 ms) |

|

|

| |

M [29 H], (1.880 ms) |

| |

Analog Video |

|

|

L [0 H], (100 ns) | O [1018 H], (64.64 ms) |

|

|

| |

| P [3 H], (190.5 | s) |

N [3 H], (190.5 | s) |

|

4. Async Reset Timing

VINIT Trigger

Q [1 H], (68.00 |

| s) |

|

| |

|

| R [9 H], (572.0 | s) |

| |

Internal VD |

|

|

|

| |

|

|

| S [1041 H], (66.10 ms) |

| |

|

| T [ 1050 H], (66.68 ms) |

| ||

|

| V [32 H], (2.040 ms) |

| ||

FDV |

|

|

|

| |

U [0 H], (32.00 | ns) |

|

| ||

|

| X [32 H], (2.040 ms) |

| ||

Digital Data |

|

|

|

| |

W [9 H], (568.0 | s) | Y [1018 H], (64.64 ms) |

| ||

|

| ||||

|

| AA [29 H], (1.880 ms) |

| ||

Analog Video |

|

|

|

| |

Z [0 H], (5 | s) | CC [1018 H], (64.64 ms) |

| ||

DD [3 H], (190.5 | s) | ||||

|

|

| |||

|

| BB [3 H], (190.5 s) |

|

| |

Operation |

|

| |||