Page 8

2.2.2 (c) Digital Output Connector (LVDS/RS-422 only)

The

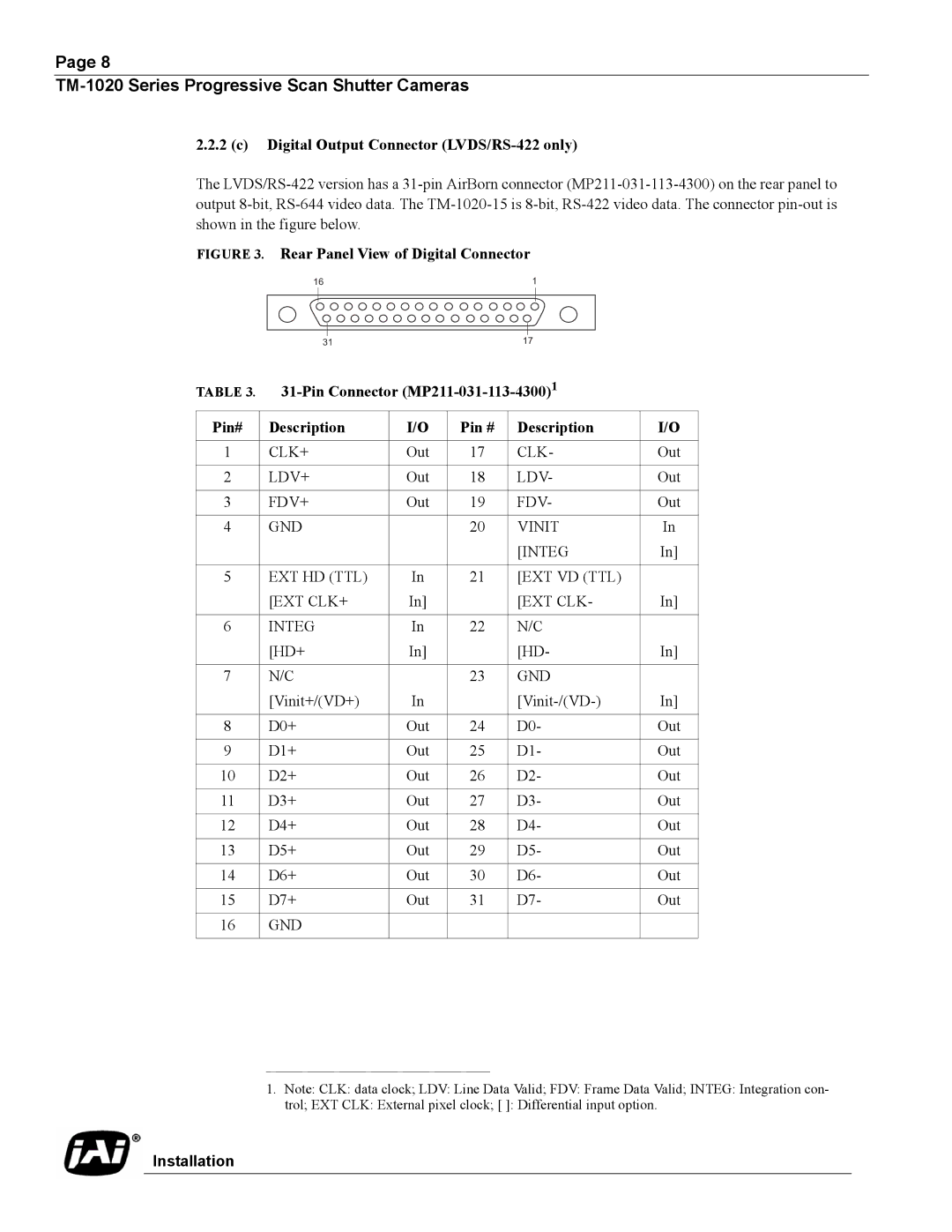

FIGURE 3. Rear Panel View of Digital Connector

| 16 |

|

|

| 1 |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 31 |

|

| 17 |

|

| |||

TABLE 3. |

| ||||||||

Pin# | Description | I/O | Pin # | Description | I/O | ||||

|

|

|

|

|

|

|

|

|

|

1 | CLK+ | Out | 17 | CLK- | Out | ||||

|

|

|

|

|

|

|

|

|

|

2 | LDV+ | Out | 18 | LDV- | Out | ||||

|

|

|

|

|

|

|

|

|

|

3 | FDV+ | Out | 19 | FDV- | Out | ||||

|

|

|

|

|

|

|

|

|

|

4 | GND |

| 20 | VINIT | In | ||||

|

|

|

|

|

| [INTEG | In] | ||

|

|

|

|

|

|

|

|

|

|

5 | EXT HD (TTL) | In | 21 | [EXT VD (TTL) |

| ||||

| [EXT CLK+ | In] |

| [EXT CLK- | In] | ||||

|

|

|

|

|

|

|

|

|

|

6 | INTEG | In | 22 | N/C |

| ||||

| [HD+ | In] |

| [HD- | In] | ||||

|

|

|

|

|

|

|

|

|

|

7 | N/C |

| 23 | GND |

| ||||

| [Vinit+/(VD+) | In |

| In] | |||||

|

|

|

|

|

|

|

|

|

|

8 | D0+ | Out | 24 | D0- | Out | ||||

|

|

|

|

|

|

|

|

|

|

9 | D1+ | Out | 25 | D1- | Out | ||||

|

|

|

|

|

|

|

|

|

|

10 | D2+ | Out | 26 | D2- | Out | ||||

|

|

|

|

|

|

|

|

|

|

11 | D3+ | Out | 27 | D3- | Out | ||||

|

|

|

|

|

|

|

|

|

|

12 | D4+ | Out | 28 | D4- | Out | ||||

|

|

|

|

|

|

|

|

|

|

13 | D5+ | Out | 29 | D5- | Out | ||||

|

|

|

|

|

|

|

|

|

|

14 | D6+ | Out | 30 | D6- | Out | ||||

|

|

|

|

|

|

|

|

|

|

15 | D7+ | Out | 31 | D7- | Out | ||||

|

|

|

|

|

|

|

|

|

|

16 | GND |

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

1.Note: CLK: data clock; LDV: Line Data Valid; FDV: Frame Data Valid; INTEG: Integration con-

trol; EXT CLK: External pixel clock; [ ]: Differential input option.

Installation