Channelized OC12 IQ PIC

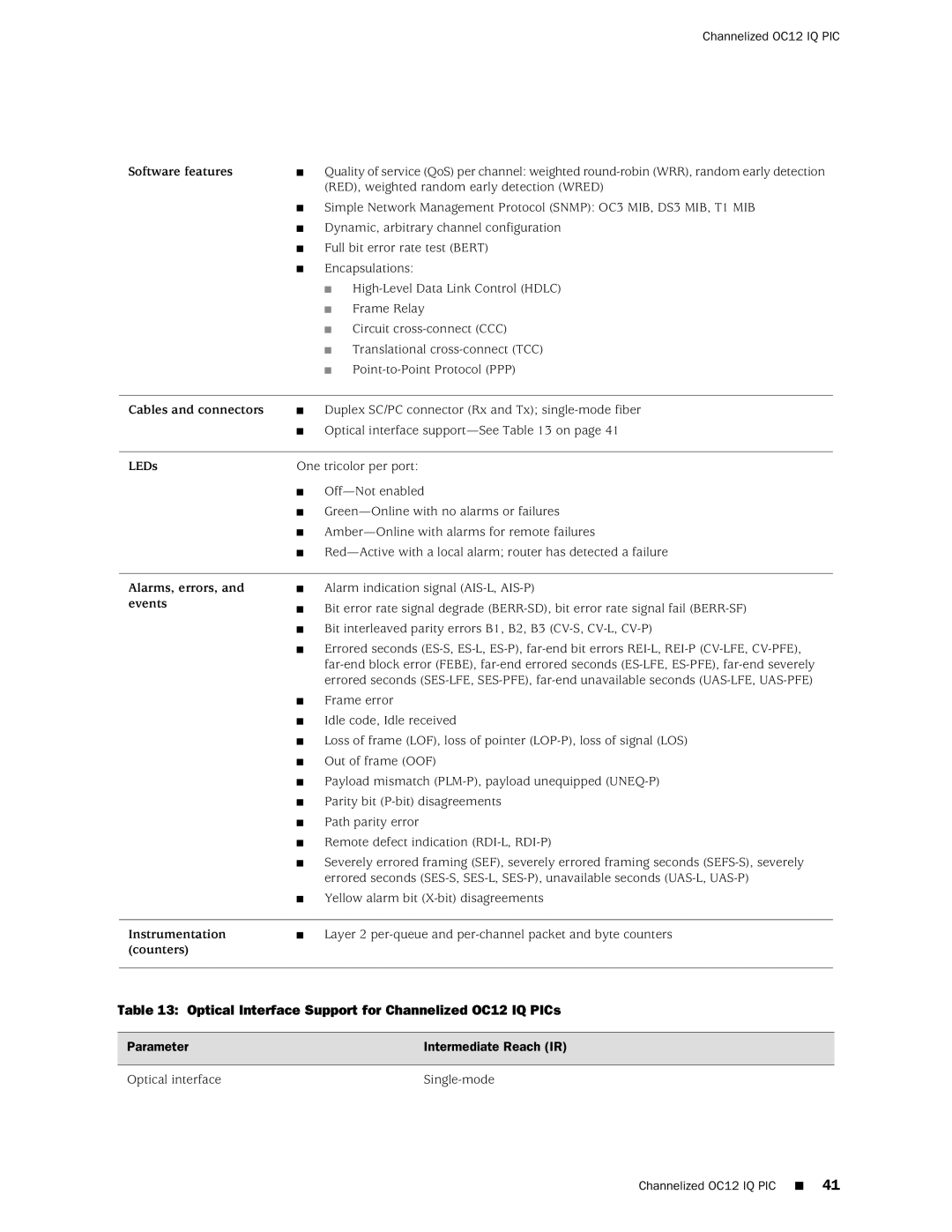

Software features

Cables and connectors

LEDs

Alarms, errors, and events

Instrumentation (counters)

■Quality of service (QoS) per channel: weighted

■Simple Network Management Protocol (SNMP): OC3 MIB, DS3 MIB, T1 MIB

■Dynamic, arbitrary channel configuration

■Full bit error rate test (BERT)

■Encapsulations:

■

■Frame Relay

■Circuit

■Translational

■

■Duplex SC/PC connector (Rx and Tx);

■Optical interface

One tricolor per port:

■

■

■

■

■Alarm indication signal

■Bit error rate signal degrade

■Bit interleaved parity errors B1, B2, B3

■Errored seconds

■Frame error

■Idle code, Idle received

■Loss of frame (LOF), loss of pointer

■Out of frame (OOF)

■Payload mismatch

■Parity bit

■Path parity error

■Remote defect indication

■Severely errored framing (SEF), severely errored framing seconds

■Yellow alarm bit

■Layer 2

Table 13: Optical Interface Support for Channelized OC12 IQ PICs

Parameter | Intermediate Reach (IR) |

Optical interface |

Channelized OC12 IQ PIC ■ 41