The APC sensor (R911) detects driving current from the drive voltage at the YGR (Q138), drive (Q921) and power (Q922) amplifiers. The detected current is converted into DC voltage at Q913, then applied to the APC control circuit (IC901, pin 2). The applied voltage is compared with a “PSET” voltage from the CPU via the D/A converter (LOGIC unit; IC5), and the APC control circuit outputs “VGGC” volt- age from pin 1 to control the YGR, drive and power ampli- fiers.

When the driving current is increased, input voltage of the differential amplifier (IC901, pin 2) will be increased. In such cases, the differential amplifier output voltage (IC901, pin 1) is decreased to reduce the driving current.

4-3 PLL CIRCUITS

4-3-1 50 MHz BAND PLL CIRCUIT (RF UNIT)

The osillated signal at the 6MVCO (Q341, D341) is amplified at the buffer amplifiers (Q342, Q343). The amplified signal is applied to the PLL IC (IC801, pin 2) via the

The signal which is applied to the PLL IC (IC801) is divided by

4-3-2 144 MHz BAND PLL CIRCUIT (VCO BOARD AND RF UNIT)

The osillated signal at the

The applied signal is divided by serial data from the CPU (N- data) and

While operating in the 144 MHz band, the lock voltage is applied to the CPU (LOGIC unit; IC1) via the tune control cir- cuit (Q803) to track the center frequency of the tunable bandpass filters (D306, D309, D310) as the “TUNE” signal.

4-3-3 440 MHz BAND PLL CIRCUIT (VCO BOARD AND RF UNIT)

The osillated signal at the

The applied signal is divided by serial data from the CPU (N- data) and

4-3-4 1200MHz BAND PLL CIRCUIT (VCO BOARD AND RF UNIT)

The osillated signal at the

The applied signal is divided by serial data from the CPU (N- data) and

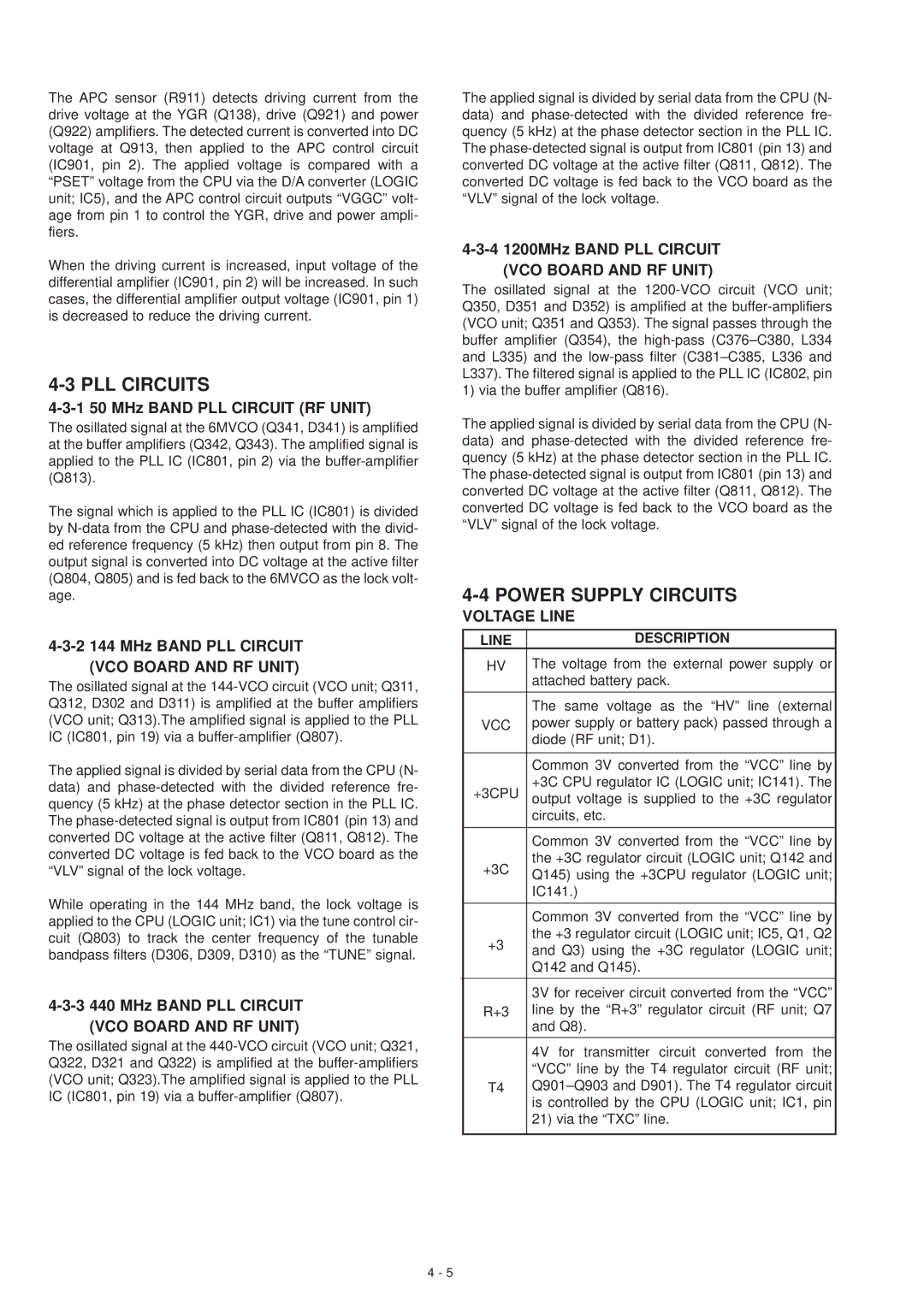

4-4 POWER SUPPLY CIRCUITS VOLTAGE LINE

| LINE | DESCRIPTION |

|

| HV | The voltage from the external power supply or |

|

|

| attached battery pack. |

|

|

|

|

|

|

| The same voltage as the “HV” line (external |

|

| VCC | power supply or battery pack) passed through a |

|

|

| diode (RF unit; D1). |

|

|

|

|

|

|

| Common 3V converted from the “VCC” line by | |

| +3CPU | +3C CPU regulator IC (LOGIC unit; IC141). The | |

| output voltage is supplied to the +3C regulator | ||

|

| circuits, etc. | |

|

|

|

|

|

| Common 3V converted from the “VCC” line by | |

| +3C | the +3C regulator circuit (LOGIC unit; Q142 and | |

| Q145) using the +3CPU regulator (LOGIC unit; | ||

|

| ||

|

| IC141.) | |

|

|

|

|

|

| Common 3V converted from the “VCC” line by | |

| +3 | the +3 regulator circuit (LOGIC unit; IC5, Q1, Q2 | |

| and Q3) using the +3C regulator (LOGIC unit; | ||

|

| ||

|

| Q142 and Q145). | |

|

|

|

|

|

| 3V for receiver circuit converted from the “VCC” | |

| R+3 | line by the “R+3” regulator circuit (RF unit; Q7 | |

|

| and Q8). | |

|

|

|

|

|

| 4V for transmitter circuit converted from the | |

|

| “VCC” line by the T4 regulator circuit (RF unit; | |

| T4 | ||

|

| is controlled by the CPU (LOGIC unit; IC1, pin | |

|

| 21) via the “TXC” line. | |

|

|

|

|

4 - 5