www.ti.comDigital Interface

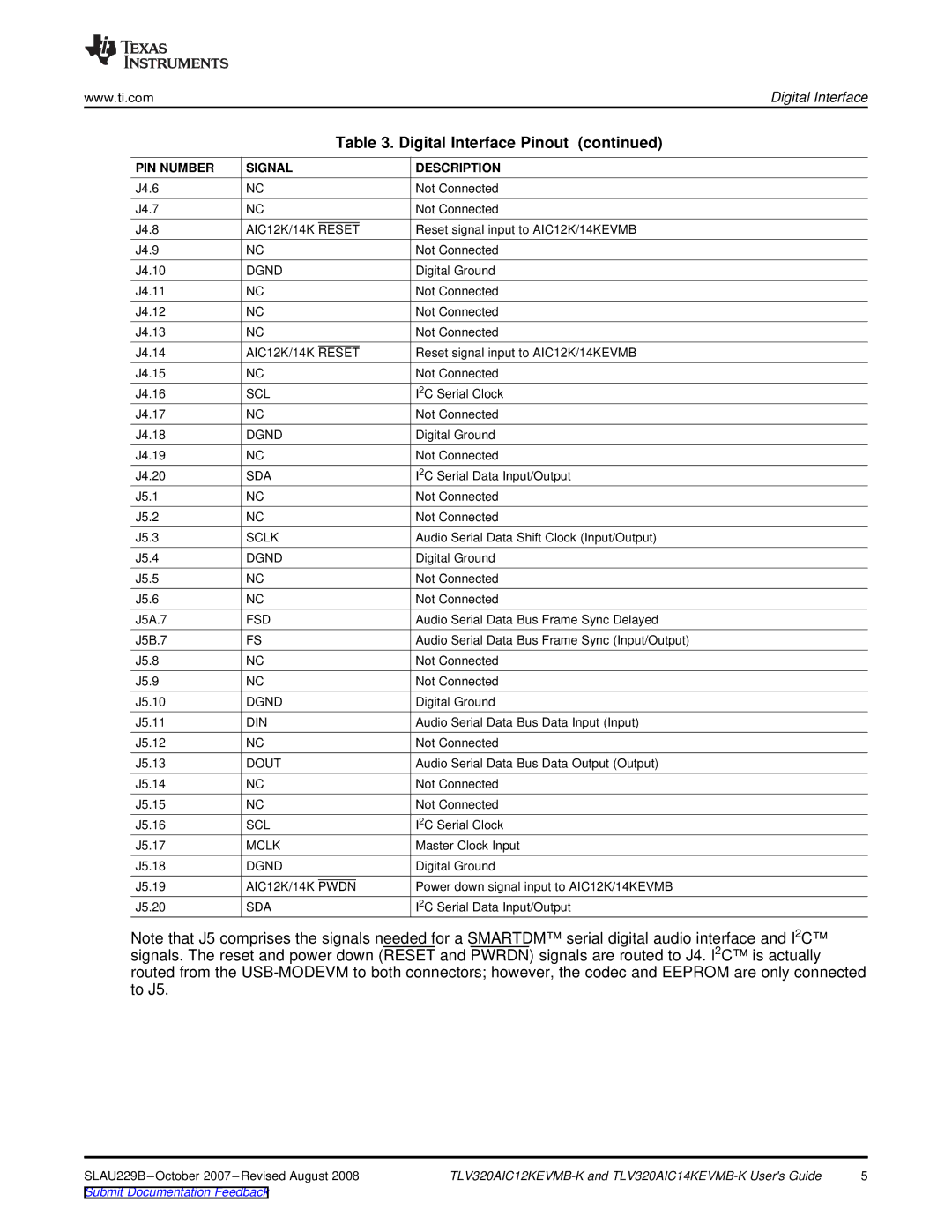

Table 3. Digital Interface Pinout (continued)

PIN NUMBER | SIGNAL | DESCRIPTION |

J4.6 | NC | Not Connected |

J4.7 | NC | Not Connected |

J4.8 | AIC12K/14K RESET | Reset signal input to AIC12K/14KEVMB |

J4.9 | NC | Not Connected |

J4.10 | DGND | Digital Ground |

J4.11 | NC | Not Connected |

J4.12 | NC | Not Connected |

J4.13 | NC | Not Connected |

J4.14 | AIC12K/14K RESET | Reset signal input to AIC12K/14KEVMB |

J4.15 | NC | Not Connected |

J4.16 | SCL | I2C Serial Clock |

J4.17 | NC | Not Connected |

J4.18 | DGND | Digital Ground |

J4.19 | NC | Not Connected |

J4.20 | SDA | I2C Serial Data Input/Output |

J5.1 | NC | Not Connected |

J5.2 | NC | Not Connected |

J5.3 | SCLK | Audio Serial Data Shift Clock (Input/Output) |

J5.4 | DGND | Digital Ground |

J5.5 | NC | Not Connected |

J5.6 | NC | Not Connected |

J5A.7 | FSD | Audio Serial Data Bus Frame Sync Delayed |

J5B.7 | FS | Audio Serial Data Bus Frame Sync (Input/Output) |

J5.8 | NC | Not Connected |

J5.9 | NC | Not Connected |

J5.10 | DGND | Digital Ground |

J5.11 | DIN | Audio Serial Data Bus Data Input (Input) |

J5.12 | NC | Not Connected |

J5.13 | DOUT | Audio Serial Data Bus Data Output (Output) |

J5.14 | NC | Not Connected |

J5.15 | NC | Not Connected |

J5.16 | SCL | I2C Serial Clock |

J5.17 | MCLK | Master Clock Input |

J5.18 | DGND | Digital Ground |

J5.19 | AIC12K/14K PWDN | Power down signal input to AIC12K/14KEVMB |

J5.20 | SDA | I2C Serial Data Input/Output |

Note that J5 comprises the signals needed for a SMARTDM™ serial digital audio interface and I2C™ signals. The reset and power down (RESET and PWRDN) signals are routed to J4. I2C™ is actually routed from the

5 |

Submit Documentation Feedback