R

Appendix

Additional Design Considerations

Package Constraints

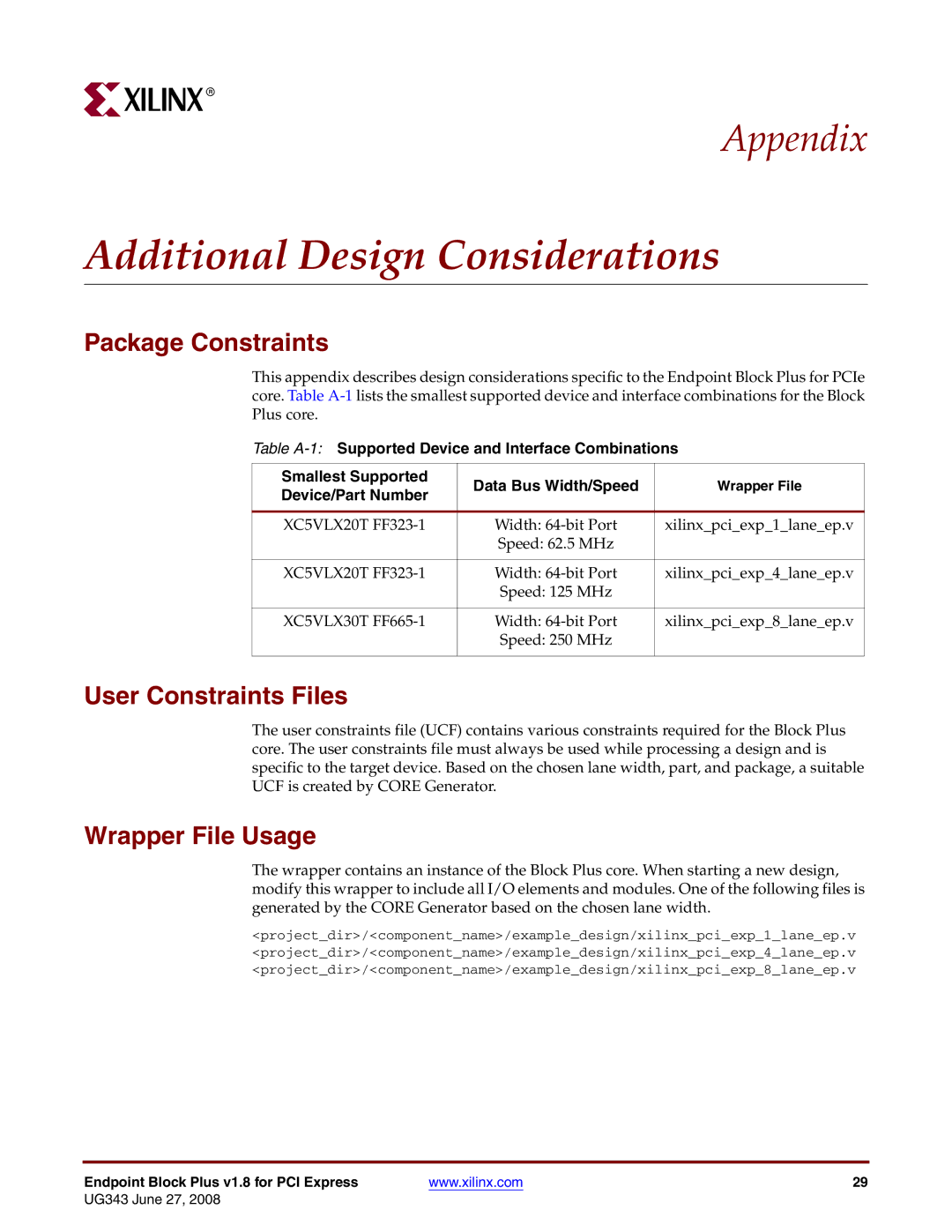

This appendix describes design considerations specific to the Endpoint Block Plus for PCIe core. Table

Table

Smallest Supported | Data Bus Width/Speed | Wrapper File | |

Device/Part Number | |||

|

| ||

|

|

| |

XC5VLX20T | Width: | xilinx_pci_exp_1_lane_ep.v | |

| Speed: 62.5 MHz |

| |

|

|

| |

XC5VLX20T | Width: | xilinx_pci_exp_4_lane_ep.v | |

| Speed: 125 MHz |

| |

|

|

| |

XC5VLX30T | Width: | xilinx_pci_exp_8_lane_ep.v | |

| Speed: 250 MHz |

| |

|

|

|

User Constraints Files

The user constraints file (UCF) contains various constraints required for the Block Plus core. The user constraints file must always be used while processing a design and is specific to the target device. Based on the chosen lane width, part, and package, a suitable UCF is created by CORE Generator.

Wrapper File Usage

The wrapper contains an instance of the Block Plus core. When starting a new design, modify this wrapper to include all I/O elements and modules. One of the following files is generated by the CORE Generator based on the chosen lane width.

<project_dir>/<component_name>/example_design/xilinx_pci_exp_1_lane_ep.v <project_dir>/<component_name>/example_design/xilinx_pci_exp_4_lane_ep.v <project_dir>/<component_name>/example_design/xilinx_pci_exp_8_lane_ep.v

Endpoint Block Plus v1.8 for PCI Express | www.xilinx.com | 29 |

UG343 June 27, 2008