Dual Core Example Design

R

simulation/tests

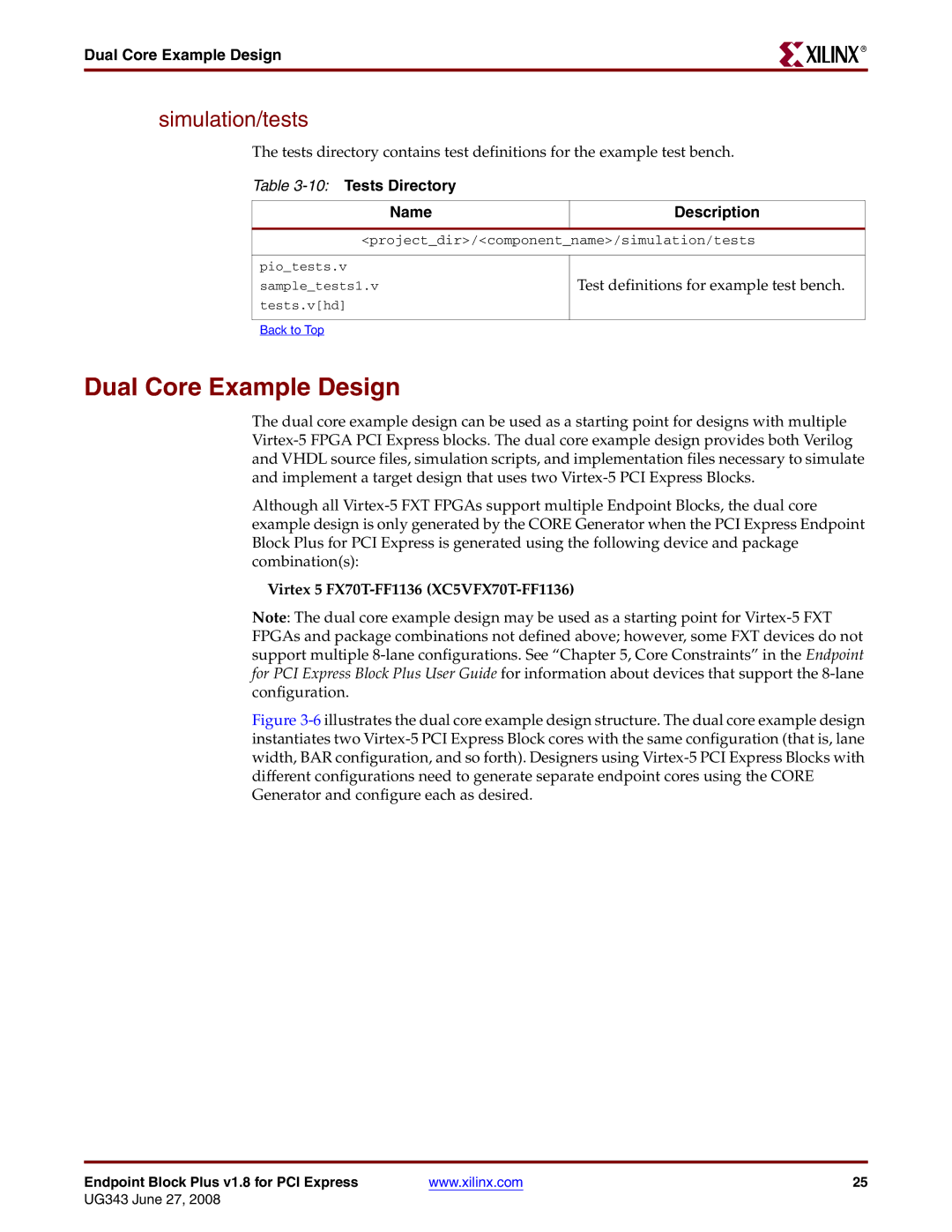

The tests directory contains test definitions for the example test bench.

Table 3-10: Tests Directory

Name | Description |

|

|

<project_dir>/<component_name>/simulation/tests | |

|

|

pio_tests.v |

|

sample_tests1.v | Test definitions for example test bench. |

tests.v[hd] |

|

|

|

Back to Top |

|

Dual Core Example Design

The dual core example design can be used as a starting point for designs with multiple

Although all

Virtex 5

Note: The dual core example design may be used as a starting point for

Figure 3-6 illustrates the dual core example design structure. The dual core example design instantiates two Virtex-5 PCI Express Block cores with the same configuration (that is, lane width, BAR configuration, and so forth). Designers using Virtex-5 PCI Express Blocks with different configurations need to generate separate endpoint cores using the CORE Generator and configure each as desired.

Endpoint Block Plus v1.8 for PCI Express | www.xilinx.com | 25 |

UG343 June 27, 2008