Dual Core Example Design

R

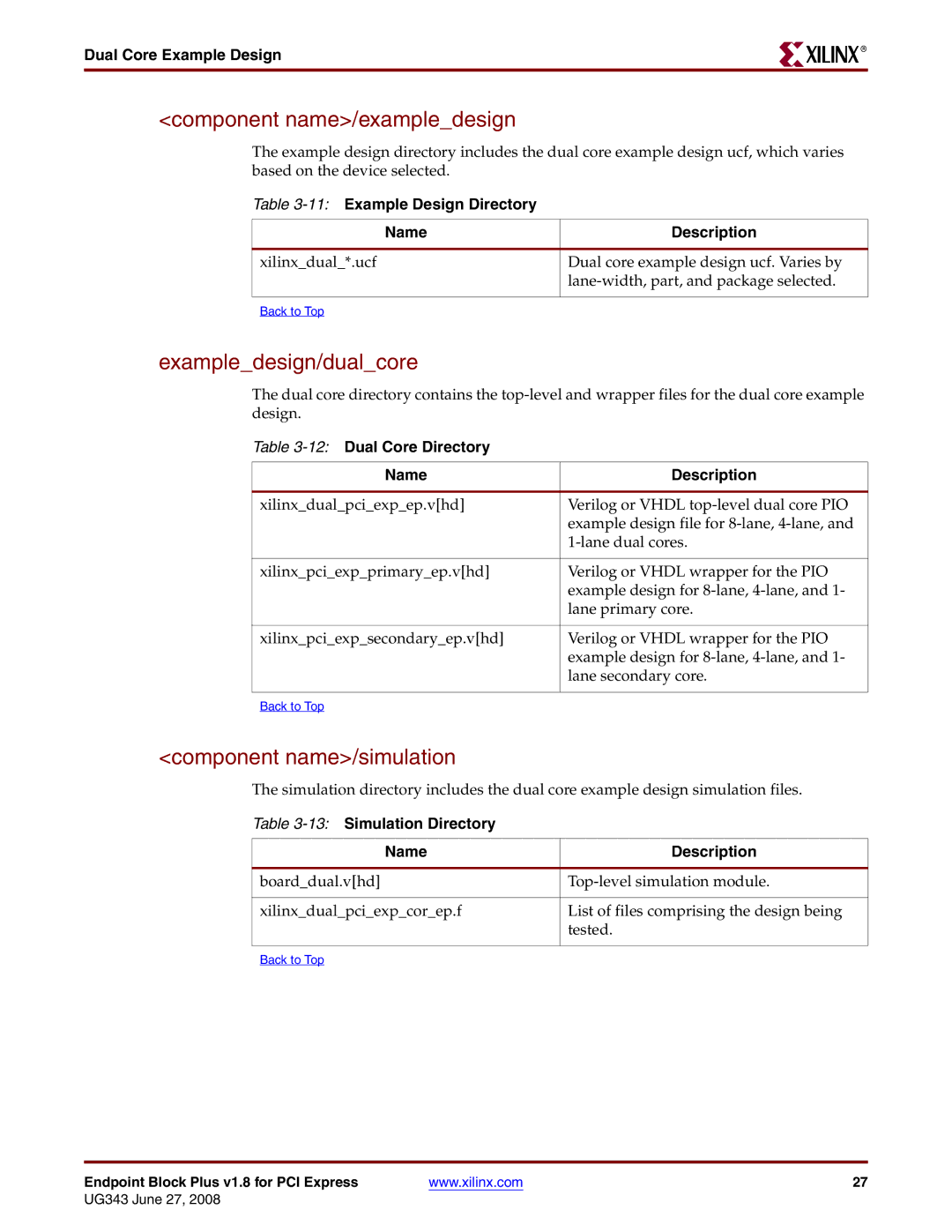

<component name>/example_design

The example design directory includes the dual core example design ucf, which varies based on the device selected.

Table 3-11: Example Design Directory

Name | Description |

|

|

xilinx_dual_*.ucf | Dual core example design ucf. Varies by |

| |

|

|

Back to Top |

|

example_design/dual_core

The dual core directory contains the

Table 3-12: Dual Core Directory

Name | Description |

|

|

xilinx_dual_pci_exp_ep.v[hd] | Verilog or VHDL |

| example design file for |

| |

|

|

xilinx_pci_exp_primary_ep.v[hd] | Verilog or VHDL wrapper for the PIO |

| example design for |

| lane primary core. |

|

|

xilinx_pci_exp_secondary_ep.v[hd] | Verilog or VHDL wrapper for the PIO |

| example design for |

| lane secondary core. |

|

|

Back to Top |

|

<component name>/simulation

The simulation directory includes the dual core example design simulation files.

Table 3-13: Simulation Directory

Name | Description |

|

|

board_dual.v[hd] | |

|

|

xilinx_dual_pci_exp_cor_ep.f | List of files comprising the design being |

| tested. |

|

|

Back to Top |

|

Endpoint Block Plus v1.8 for PCI Express | www.xilinx.com | 27 |

UG343 June 27, 2008