R

Chapter 3: Quickstart Example Design

•routed.sdf

Timing model Standard Delay File.

•mapped.mrp

Xilinx map report.

•routed.par

Xilinx place and route report.

•routed.twr

Xilinx timing analysis report.

The script file starts from an EDIF/NGC file and results in a bitstream file. It is possible to use the Xilinx ISE GUI to implement the example design. However, the GUI flow is not presented in this document.

Directory Structure and File Contents

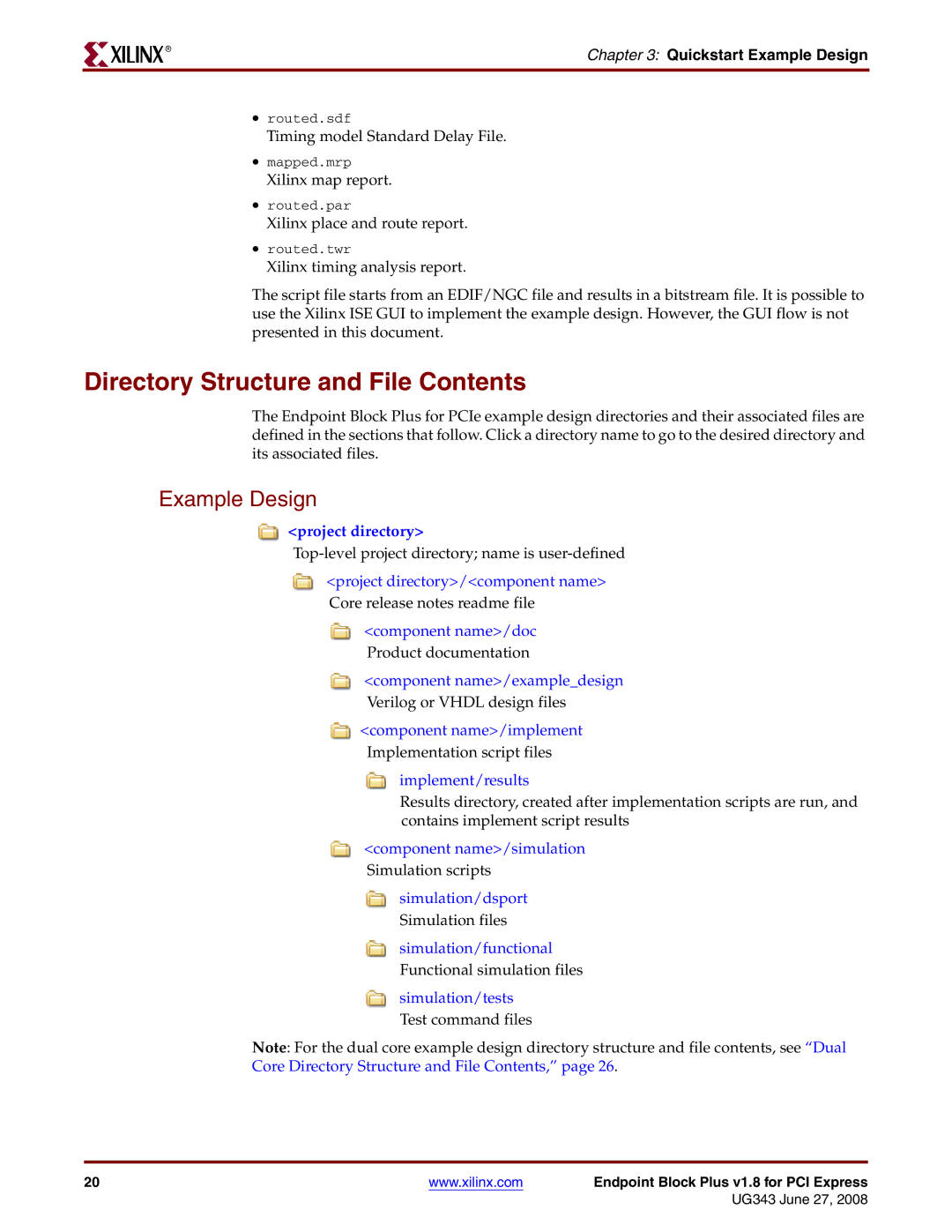

The Endpoint Block Plus for PCIe example design directories and their associated files are defined in the sections that follow. Click a directory name to go to the desired directory and its associated files.

Example Design

![]() <project directory>

<project directory>

![]() <project directory>/<component name>

<project directory>/<component name>

Core release notes readme file

![]() <component name>/doc

<component name>/doc

Product documentation

![]() <component name>/example_design

<component name>/example_design

Verilog or VHDL design files

![]() <component name>/implement

<component name>/implement

Implementation script files

![]() implement/results

implement/results

Results directory, created after implementation scripts are run, and contains implement script results

![]() <component name>/simulation

<component name>/simulation

Simulation scripts

![]() simulation/dsport

simulation/dsport

Simulation files

![]() simulation/functional

simulation/functional

Functional simulation files

![]() simulation/tests

simulation/tests

Test command files

Note: For the dual core example design directory structure and file contents, see “Dual Core Directory Structure and File Contents,” page 26.

20 | www.xilinx.com | Endpoint Block Plus v1.8 for PCI Express |

|

| UG343 June 27, 2008 |