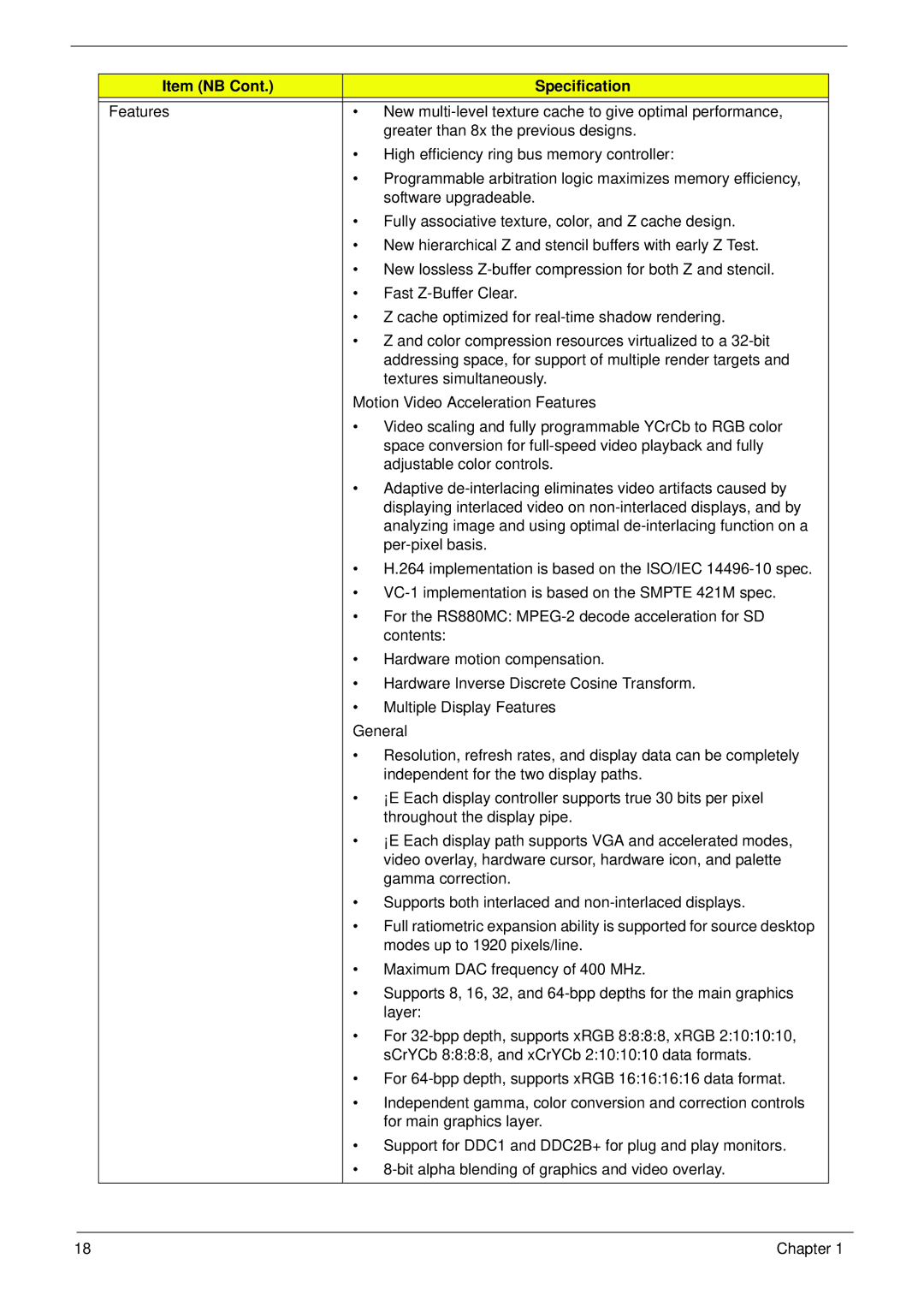

Item (NB Cont.) |

| Specification |

|

|

|

Features | • | New |

|

| greater than 8x the previous designs. |

| • High efficiency ring bus memory controller: | |

| • Programmable arbitration logic maximizes memory efficiency, | |

|

| software upgradeable. |

| • Fully associative texture, color, and Z cache design. | |

| • New hierarchical Z and stencil buffers with early Z Test. | |

| • New lossless | |

| • Fast | |

| • Z cache optimized for | |

| • Z and color compression resources virtualized to a | |

|

| addressing space, for support of multiple render targets and |

|

| textures simultaneously. |

| Motion Video Acceleration Features | |

| • Video scaling and fully programmable YCrCb to RGB color | |

|

| space conversion for |

|

| adjustable color controls. |

| • Adaptive | |

|

| displaying interlaced video on |

|

| analyzing image and using optimal |

|

| |

| • H.264 implementation is based on the ISO/IEC | |

| • | |

| • For the RS880MC: | |

|

| contents: |

| • | Hardware motion compensation. |

| • Hardware Inverse Discrete Cosine Transform. | |

| • | Multiple Display Features |

| General | |

| • Resolution, refresh rates, and display data can be completely | |

|

| independent for the two display paths. |

| • ¡E Each display controller supports true 30 bits per pixel | |

|

| throughout the display pipe. |

| • ¡E Each display path supports VGA and accelerated modes, | |

|

| video overlay, hardware cursor, hardware icon, and palette |

|

| gamma correction. |

| • Supports both interlaced and | |

| • Full ratiometric expansion ability is supported for source desktop | |

|

| modes up to 1920 pixels/line. |

| • Maximum DAC frequency of 400 MHz. | |

| • Supports 8, 16, 32, and | |

|

| layer: |

| • For | |

|

| sCrYCb 8:8:8:8, and xCrYCb 2:10:10:10 data formats. |

| • For | |

| • Independent gamma, color conversion and correction controls | |

|

| for main graphics layer. |

| • Support for DDC1 and DDC2B+ for plug and play monitors. | |

| • | |

|

|

|

18 | Chapter 1 |